Decimation is a widely used digital signal processing technique that is employed in various telecommunication fields [1-3]. For a decimation chain to cover multiple bands of cellular telecommunication standards, such as UTRA/FDD, DCS1800, PCS1900, GSM850, and E-GSM900, the chain may bear a polynomial interpolator, which adjusts various sample rates from a multirate oversampling analog-to-digital converter (ADC) to a fixed data rate chosen by the standard under consideration. A good range at the input of the decimation chain is chosen to be more than 289–362 MHz in order to cover multiple bands while the chain finally outputs two sample rates, namely 3.84 MHz and 270.83 kHz, for UTRA/FDD and GSM, respectively. Assuming that the ADC clock (CK) rate is a nominal 312 MHz by default, we find that the oversampling ratio for WCDMA is about 81 with a possible signal-to-noise ratio (SNR) of >70 dB under jitter-free conditions. In turn, an SNR of about 90 dB is attainable for GSM under the same CK rate conditions.

In this paper, alternative configurations for the decimation chain in multi-standard reconfigurable radios [4-6] are explained and compared from the perspective of covering the 1.9-GHz and 900-MHz frequency bands. The errors incurred by the use of the Lagrange polynomial interpolator are estimated in order to gain insight into the tradeoff between aliasing and the signal bandwidth (BW). Further, the operation of the decimation chain in the compressed mode or a discontinuous transmission is addressed in order to guarantee continuous packet connectivity (CPC).

II. ALTERNATIVE CONFIGURATIONS FOR THE DECIMATION CHAIN

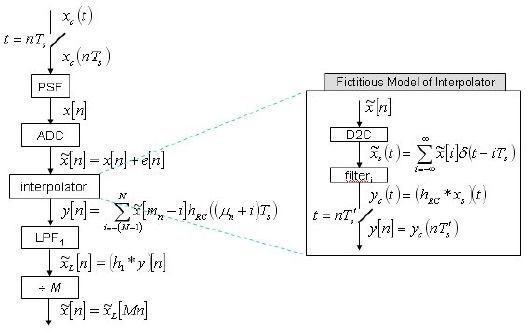

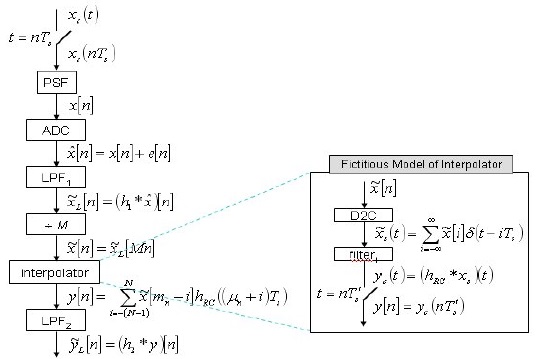

Two configurations of building-block placement are considered for the decimation chains with data interpolators. Configuration I, shown in Fig. 1, has the interpolator immediately after the ADC, whereas Configuration II, shown in Fig. 2, has the interpolator located after the decimation-by-M (=24) block. Configuration I needs a faster interpolator. The PSF is a pulse shaping filter; here, a root raised cosine filter with a roll-off factor of 0.22 is used for the 1.9-GHz band, while a Gaussian low-pass filter with a normalized BW of 0.5 is used for the 900-MHz band, with no clock jitter assumed. If the roll-off factor drops, the BW becomes more compact. If the normalized BW drops, the intersymbol interference increases but the BW becomes more compact. After a second-order discrete-time delta-sigma ADC is passed, the signal is corrupted with the quantization noise

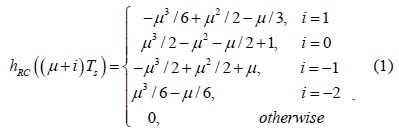

In Figs. 1 and 2, the interpolator is based on a fictitious model consisting of a discrete-to-continuous (D2C) block and an interpolating filter, filteri, whose impulse response is denoted as

The overall chains in Configuration I shown in Fig. 1 and Configuration II illustrated in Fig. 2 are fed with

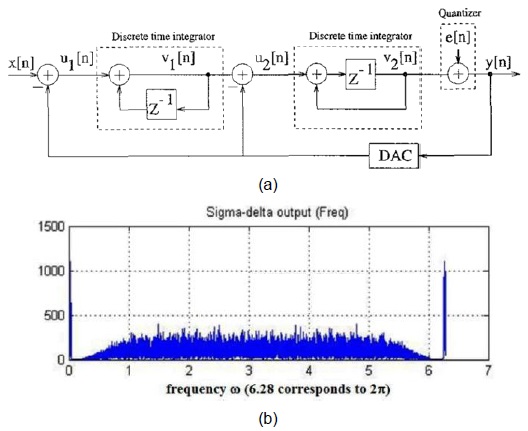

The delta-sigma ADC in Figs. 1 and 2 is modeled such that the overall noise is

A single-tone input near dc, together with random noise, which is calculated from the set SNR and oversampling ratio, is applied at the ADC input. The corresponding spectral-domain output of the ADC is obtained from a simulation and plotted in Fig. 3(b), which exhibits the expected noise shaping behavior of the delta-sigma ADC. A Hanning window is used for obtaining the output power spectral density. Low-pass filters, LPF1 and LPF2 , are modeled as brick-wall filters, and hence,

III. POLYNOMIAL INTERPOLATOR AND INTERPOLATION ERROR

Configuration I shown in Fig. 1 uses the interpolator to adjust the variable sample rates to 312 MHz, while Configuration II illustrated in Fig. 2 uses it to adjust finally to 13 MHz. The final output sample rates for Configurations I and II are 13 MHz. Among various interpolator types, the Lagrange interpolator is adopted in view of the tradeoff between practicality and performance. From the fictitious model shown in Figs. 1 and 2 and with the introduction of three variables,

As the summation index

For various

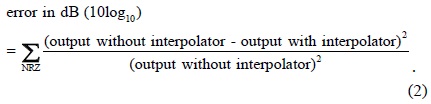

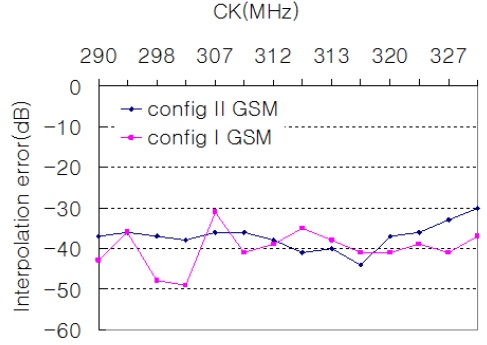

From a simulation of the process of obtaining the spectrum of this newly introduced interpolation error, we verified that practical polynomial interpolators have aliases that are not of the white noise type but are close to the signal BW. These aliases lead to the interpolation error defined above. From extensive simulations, interpolation errors for various 1/

Thus, we can conclude and verify from the simulated results illustrated in Figs. 5 and 6 that Configuration II exhibits better performance than Configuration I in terms of the variability of the interpolation error over the input sample rates of interest. Furthermore, the following is verified from the simulated results shown in Figs. 5 and 6, on the basis of the newly defined interpolation error: Since the ratio of the sampling frequency to the signal BW for WCDMA is considerably lower than that for GSM, the average interpolation error is significantly larger for WCDMA than for GSM. On the basis of the facts that the variability of the interpolation error is smaller and the operation speed demanded is lower for Configuration II than for Configuration I, Configuration II is chosen to be a better solution; the SNR at its overall output is computed to be more than 30 dB, meeting the SNR requirements of the given cellular standards.

IV. SELF-TIMING ADJUSTMENT FOR CPC

The scenario considered in this section is as follows: If the multi-standard multi-band radio receiver based on the multirate ADC and the decimation chain switches its radio access technology or its channel band from one to another, it has to undergo CK-domain crossing if the sample rate of the ADC is directly coupled to the local oscillator (LO) frequency. To guarantee the so-called CPC regarding information transmission, a remedy is needed in the case of the (band) switching mentioned above. In this section, the remedy is accounted for in the context of the compressed mode of operation in WCDMA, but without any loss of generality, it may be applied to discontinuous transmission and reception, idle mode, and slotted mode in other standards as well.

To guarantee CPC, during the compressed mode of operation, precise timing should not be lost despite the shutdown of the radio transceiver in the mobile device for some time. For WCDMA, precise timing means better than 1/16 of the chip (about 16.276 ns) for 64-QAM. In the case of the compressed mode, the interpolator loses track of the input positions, and the subsequent resetting of the interpolator at the end of the mode will cause some phase error that might be large compared with the error bound dictated by the path searcher or the rake receiver. Since reinitialization of the searcher is known to take more than 100 ms, resetting the path searcher in sync with the interpolator usually causes severe loss of information and hence, throughput degradation. Accordingly, the interpolator should meet the limitation of the sampling phase error or the input timing error imposed by the modem. If the phase error for every CK-domain crossing resulting from the com-pressed mode meets the requirement by the modem, the path searcher can reuse the previously acquired per-finger time delays at the end of the compressed-mode gap, which accomplishes CPC and no throughput loss.

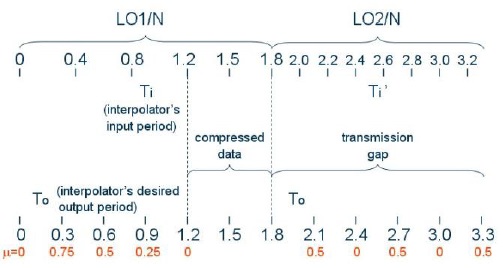

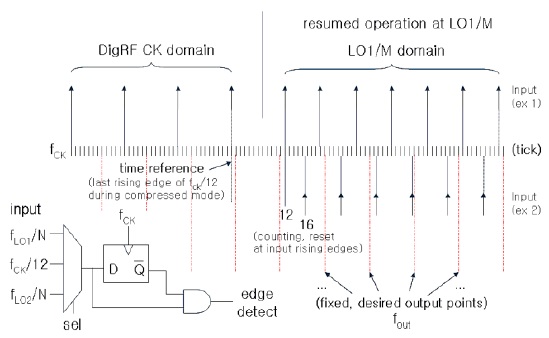

A simple and practical example of CK-domain crossing caused by the switching from one radio access technology or channel band to another is illustrated in Fig. 7. The interpolator time frame is plotted in Fig. 7 in view of the compressed mode, where

The

A stable and higher-frequency internal CK such as the DigRF CK in the radio chip is utilized to serve as a timing reference and to attain a smooth transition from one CK domain to another. DigRF is the de facto standard for the link interface between the radio chip and the baseband modem chip. In the context of the case shown in Fig. 7, the remedy for CPC is explained as follows: Switch the CK from LO1/N to the DigRF CK before entering the LO2/N CK domain for the compressed mode. This is to resolve the sync issue during the settling of the LO phase-locked loop to a new frequency, which may usually take >100 μs. The switching shall be synchronized to a submultiple of the LO1/N CK edge to meet the sampling phase error mandated by the path searcher. During the DigRF CK mode, the interpolator updates the values of

A simple method to detect the sample phase error at a clock boundary by using a CK at a high frequency,

If the data are in the LO1/M domain, then the

Decimation chain structures for dual-band radio receivers are modeled, and two alternative configurations are analyzed in terms of signal BW and aliasing. With the introduction of a new criterion, the interpolation error, the performances of the alternative configurations are analyzed and compared for both 1.9-GHz UTRA/FDD and 900-MHz GSM bands, which provides insight into the origin of aliases and the tradeoff between aliasing and signal BW. Each configuration is modeled with a cubic Lagrange interpolator in conjunction with a multirate delta-sigma ADC, targeted for a multi-standard multi-band reconfigurable radio. The sample rate processor is further extended to cover the issue of inter-radio-technology or inter-channel switching, which gives rise to CK-domain crossing. A remedy is proposed to deal with this issue, thereby maintaining CPC in the compressed mode of operation in WCDMA and in practically equivalent modes in other standards.