In this paper, a 50ns 256-kb EEPROM IP for MCU (micro controller unit) ICs is designed. The speed of data sensing is increased in the read mode by using a proposed DB sensing circuit of differential amplifier type which uses the reference voltage, and the switching speed is also increased by reducing the total DB parasitic capacitance as a distributed DB structure is separated into eight. Also, the access time is reduced reducing a precharging time of BL in the read mode removing a 5V NMOS transistor in the conventional RD switch, and the reliability of output data can be secured by obtaining the differential voltage (ΔV) between the DB and the reference voltages as 0.2*VDD. The access time of the designed 256-kb EEPROM IP is 45.8ns and the layout size is 1571.625μm × 798.540μm based on MagnaChip's 0.18μm EEPROM process.

비휘발성 메모리 IP는 스마트 카드와 비접촉 카드, 모바일 통신, 자동화 응용제품의 MCU(Micro Controller Unit) 등의 광범위한 SoC(System on Chip) 분야에 사용되고 있으며 고속의 읽기와 쓰기동작 및 저 전력 소비의 특성을 가진 비휘발성 메모리가 요구되고 있다[1,2]. 실시간 정보 갱신, 보안 데이터 저장, 명령코드 저장 등의 기능을 하는 MCU용 내장형 비휘발성 메모리로 명령 코드 저장용인 OTP(One-Time Programmable) 메모리와, 사용자 데이터 저장을 위한 내장형 EEPROM 메모리가 사용되고 있으며 1Mb 이하의 비휘발성 메모리로는 EEPROM이 주로 사용되고 있다[3].

기존의 EEPROM의 설계 기술 동향으로는 저면적, 저전력, 고속의 설계기술이 제안되었다. 저면적 EEPROM 설계 기술은 SSTC EEPROM 셀이 제안되었고[4], EEPROM 셀 어레이에서 매 word 단위로 분리되었던 HPW (High-Voltage P-Well)을 동작 모드별 동일한 바이어스 전압이 인가되는 인접한 2 워드(word) 단위로 HPW을 공유하여 EEPROM 셀 어레이의 면적을 줄였다[5]. 그리고 저전력 설계기술로는 대기전류(stand-by) 전류를 줄이기 위해 기준전압 발생기 회로가 필요 없는 디지털 센싱 방식의 DB 센싱 회로, 저전력 DC-DC 변환 회로 설계가 제안되었다[6]. 또한 고속의 동작을 구현하기 위해 distributed DB (Data Bus) 방식의 회로 설계 기술이 제안되었다[4]. 그리고 EEPROM Function 테스트 시 테스트 시간을 줄이기 위해 32 워드(=512bit)의 페이지 버퍼 회로를 사용하였다. 한편 EEPROM 셀의 VT 변도(variation)을 보증(guarantee)해주기 위해 웨이퍼 테스트 시 VT shift 만큼 감안한 외부 VRD 전압으로 EEPROM 셀을 read하는 Write-Verify-Read 모드가 제안되었다[5].

본 논문에서는 50ns의 액세스 시간을 갖는 고속의 256Kb EEPROM IP(Intellectual Property)를 설계하였다. 고속의 EEPROM을 구현하기 위해 기준전압을 사용한 차동증폭기 형태(Differential Amp Type)의 DB 센싱 회로를 제안하여 액세스 시간을 줄였으며, 8개로 분리된 Distributed DB 구조를 적용하여 DB의 기생하는 커패시턴스 성분을 줄여 스위칭 속도를 높였다. 또한 기존의 RD 스위치 회로에서 Native 트랜지스터의 Off-leakage 전류를 줄이기 위해 사용된 5V NMOS 트랜지스터를 제거함으로써 BL의 프리차지 시간을 줄이고 DB의 센싱 전압(ΔV)을 확보해 고속의 안정적인 동작이 가능하도록 하였다. 설계된 256Kb EEPROM IP의 액세스 시간은 45.8ns이고 매그나칩반도체 0.18μm EEPROM 공정으로 설계되었으며, 레이아웃 면적은 1571.625μm × 798.540μm이다.

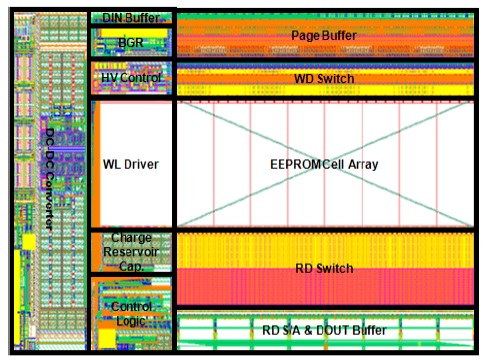

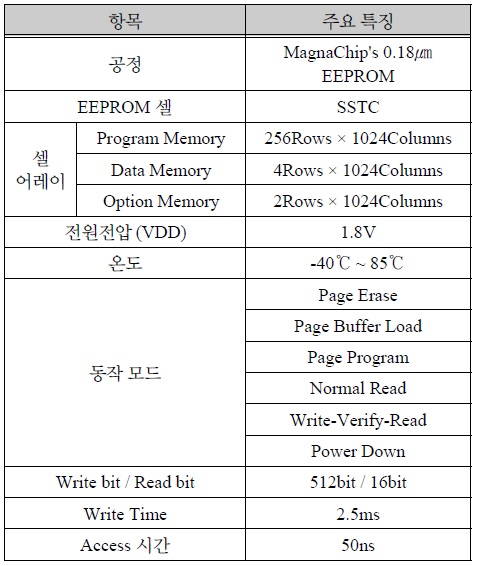

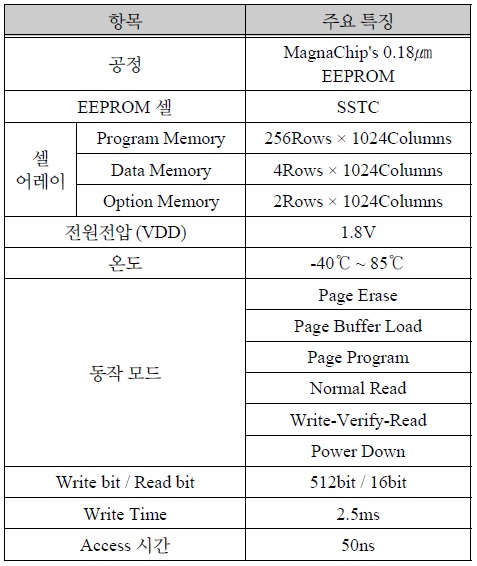

매그나칩반도체 0.18㎛ EEPROM 공정을 사용하여 설계된 256Kb EEPROM IP의 주요 특징은 표 1과 같다. SSTC(Side-wall Selective Transistor Cell)[4] 구조의 EEPROM 셀을 사용하였으며, VDD 전압은 1.8V이고, 온도 범위는 -40℃ ~ 85℃ 이다. 동작 모드는 page erase, page buffer load, page program, normal read, writeverify-read 모드가 있다. Page erase와 page program은 32 워드 단위로 수행되며, page buffer load와 read 동작은 워드 단위로 이루어진다.

[표 1.] 50ns 256Kb EEPROM IP의 주요 특징

50ns 256Kb EEPROM IP의 주요 특징

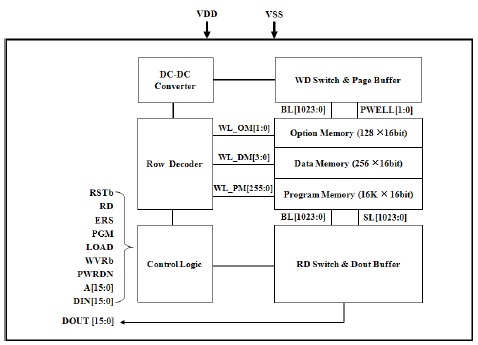

설계된 50ns 256Kb EEPROM IP는 그림 1의 블록도에서 보는 바와 같이 program memory, data memory, option memory 영역으로 구분되며, Write 테스트 시간을 줄이기 위해 32 워드의 페이지 버퍼(page buffer)를 사용하였다[5]. 행 디코더(row decoder)는 행 어드레스(row address) A[15:6]를 디코딩하여 각 메모리 영역의 WL(Word-Line)인 WL_PM[255:0], WL_DM[3:0], WL_OM[1:0] 중 한 WL을 활성화 시킨다. Page buffer load 모드에서 열 어드레스(column address) A[4:0]는 입력된 워드 데이터 DIN[15:0]를 페이지 버퍼에 load하기 위해 사용된다. 그리고 read 모드에서 열 어드레스 A[5:0]는 RD(Read Data) 스위치를 통해 선택된 WL에 연결된 64 워드 셀 중 선택된 워드 셀의 데이터를 출력하기 위해 사용된다. DOUT 버퍼는 RD S/A(sense amplifier)와 Dout 버퍼로 구성되어 있으며, 선택된 워드 셀의 데이터가 RD S/A를 통해 센싱된 후 Dout 버퍼를 통해 DOUT[15:0] 포트로 출력시킨다. 그림 1의 제어 로직 블록(control logic block)은 동작 모드에 따라 EEPROM 내부 회로에 필요한 제어 신호를 발생시킨다. DC-DC 변환기는 EEPROM 셀의 read 모드에 필요한 VRD (read voltage) 전압 및 write 모드에 필요한 VPP와 VPPL 전압을 공급한다. 인터페이스 신호는 크게 제어 신호 (RSTb, PWRDN, RD, ERS, PGM, LOAD와 WVRb), 어드레스 A[15:0] 신호, 입력데이터 DIN[15:0]와 출력 데이터 DOUT[15:0] 신호가 있다.

그림 2는 기존의 Digital DB 센싱 회로로써 읽기 동작 시 DB를 VDD로 프리차징 시키는 Low Impedance 풀-업 트랜지스터 (MP1)와 데이터 ‘1’로 프로그램된 EEPROM 셀을 읽을시 발생하는 DB의 누설 전류에 의한 전압 강하를 제거하기위해 사용된 High Impedance 풀-업 트랜지스터(MP0) 및 DB에 전달된 데이터를 DOUT으로 출력하고 래치에 저장하는 Negative Level Sensitive D-래치 로 구성되어 있다. 디지털 DB 센싱 회로는 별도의 기준전압이 필요없어 전력소모가 작으며 회로가 상대적으로 간단하여 저면적을 필요로 하는 장점이 있다[4]. 그러나 데이터 센싱 방식이 Clocked Inverter의 VIH(Input High Voltage) 및 VIL(Input Low Voltage) 전압을 이용하기 때문에 DB 전압이 VIH 이상 올라가거나 VIL 이하로 떨어져야만 정확한 데이터 센싱이 가능하다. 기존 RD S/A회로의 Clock Inverter의 Normalize된 VIL과 VIH 값은 각각 0.417, 0.687이며 ‘0’으로 프로그램된 EEPROM 셀의 경우 Normalize된 DB 전압이 0.417 이하로 떨어져야만 센싱이 가능하며 여기에 센싱 여유를 고려할 경우 더 낮은 전압에서 센싱이 이루어지게 된다. 이러한 경우 DB 전압이 충분히 방전될 때까지 시간이 필요하므로 액세스 시간이 50ns 이하의 고속 동작을 요구하는 EEPROM에서 사용하기에는 적합하지 않다.

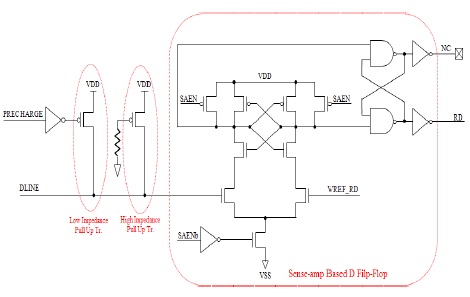

그림 3은 제안된 차동증폭기 형태의 DB 센싱 회로로써 PMOS 풀-업 트랜지스터와 센스 증폭기 기반의 D Flip-Flop 회로로 구성되어있다. 센스 증폭기 기반의 D Flip-Flop 회로의 입력단에는 DB가 연결되고 차동 입력으로는 0.75 VDD의 기준전압이 인가되어 DB 전압과 기준전압의 차가 발생하여 차동 입력전압이 변하기 시작할 때 SAENb (Sense Amplifier ENable bar) 신호에 의해 센스 증폭기가 동작하여 작은 입력전압 차를 증폭시켜 출력단으로 내보내게 된다. 차동 증폭기의 출력은 D Filp-Flop 입력단과 연결되어 DB 전압이 기준 전압 이상일 때에는 출력으로 VDD를, 기준전압 이하일 때에는 0V가 출력되게 된다. 차동 증폭기 형태의 DB 센싱 회로는 DB 전압과 차동 입력인 기준전압의 차를 증폭하는 방식을 사용하여 고속의 데이터 센싱이 가능하다.

그림 4에 4개로 분리된 DB 구조와[4] 8개로 분리된 DB 구조를 나타내었다. 동작 속도에 영향을 미치는 DB의 기생하는 커패시턴스 성분은 주로 DB의 Interconnect 커패시턴스 및 5V NMOS의 접합 커패시턴스, 게이트 overlap 커패시턴스 성분으로 구성되어있다. 그림 4(a)의 4개로 분리된 DB 구조[4] 에서는 56.6fF의 Interconnect 커패시턴스와 12.9fF의 접합 커패시턴스와 0.817fF의 게이트 overlap 커패시턴스를 가지는 5V NMOS 트랜지스터가 16개 연결되어 있어 전체 기생하는 커패시턴스는 276.3fF 정도이다. 본 논문에서는 8개로 분리된 DB 구조를 사용하여 DB의 Interconnect 커패시턴스를 32fF 정도로 줄였으며 8개의 5V NMOS 트랜지스터가 연결되어 전체 기생하는 커패시턴스를 약 절반 정도인 141.816fF로 줄여 DB 방전(discharging) 시간 감소에 따른 고속 데이터 센싱이 가능하도록 하였다.

그림 5(a)는 기존의 RD 스위치[4] 회로로써 EEPROM IP가 읽기 모드에서 동작할 때 열 어드레스에 의해 선택된 BL을 DB로 연결시켜 EEPROM 셀의 데이터를 RD S/A로 전달하는 역할을 한다. EEPROM IP가 쓰기 모드에서 동작할 때 BL에는 VPP(=14V) 또는 VPPL(=11V)과 같은 고전압이 인가되기 때문에 스위칭 트랜지스터로는 고전압을 보증할 수 있는 Native HV NMOS 트랜지스터가 사용되었으며, Native 트랜지스터의 특성상 0.3V 정도의 낮은 문턱 전압(threshold voltage) 값을 갖기 때문에 VDDP(=3.15V) 전압으로 구동될 경우 최대 1.98V의 VDD의 전압이 인가되는 BL과 DB를 VT 손실없이 전달할 수 있다.

또한 지우기 모드에서 BL에 14V가 인가되고 DB는 VDD 전압으로 프리차지된 경우 Off 된 Native HVNMOS 트랜지스터를 통해 81nA(10pA/㎛ × 8㎛ × 1024EA) 정도의 Off-Leakage 전류가 흐르게 된다. 기존의 회로에서는 저전력 특성을 확보하기 위해 Off-Leakage 전류를 줄이기 위한 방법으로써 5V NMOS 트랜지스터를 직렬로 연결하여 Off-leakage 전류를 9.2nA(3pA/㎛ × 3㎛ × 1024EA) 수준으로 낮추었다[4]. 그러나 5V NMOS 트랜지스터를 추가로 사용함으로써 스위치를 통해 흐르는 On 전류가 줄어들게 되어 BL의 VDD 프리차징 시간이 늘어나 프리차징 구간 동안 BL 전압이 VDD 전압까지 도달하지 못하는 단점이 있다. 이러한 현상으로 인해 ‘1’로 프로그램 된 EEPROM 셀을 읽는 경우 DB의 전압강하로 인해 안정적인 데이터 센싱이 불가능하게 된다. 이러한 문제점을 해결하기 위해 본 논문에서는 그림 5(b)의 5V NMOS 트랜지스터를 제거한 RD 스위치 회로를 사용하므로 BL 프리차징 속도를 높여 기존의 33.3ns 였던 프리차징 시간을 20ns로 줄여 액세스 시간을 빠르게 하였다. 또한 ‘1’로 프로그램된 EEPROM 셀을 읽는 경우 발생하는 DB의 전압강하현상을 제거하여 안정적인 데이터 센싱이 가능하도록 하였다.

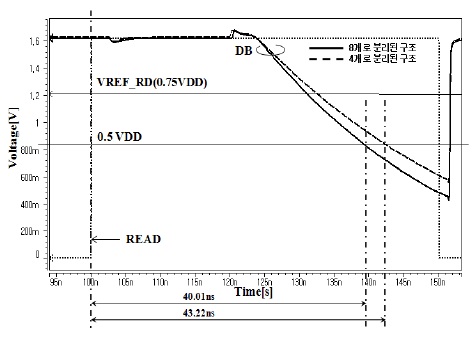

그림 6은 VDD=1.62V, VDDP=3.0V, Temp.=85℃, slow 모델 파라미터의 모의실험 조건에서 Distributed DB 구조별 모의실험 결과를 보여주고 있다. 기준전압은 0.75VDD 이며 DB 센싱전압을 확보하기 위해 0.5VDD 전압에서 SAENb 신호에 의해 센싱 되도록 설계하였다. 0.5VDD 전압 기준 4개로 분리된 구조와 8개로 분리된 구조의 DB 방전 시간은 각각 43.22ns와 40.01ns 으로 약 3.21ns 정도 줄었다.

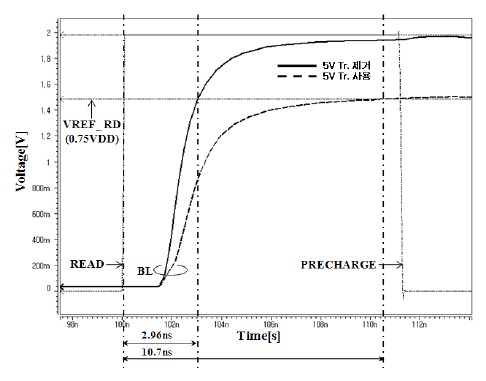

그림 7에 RD 스위치의 5V NMOS 트랜지스터 유무에 따른 BL 프리차징 모의실험 결과를 나타내었다. 프리차징 시간 동안 RD 스위치 회로에 5V NMOS 트랜지스터가 사용된 경우와 제거한 경우 BL의 전압이 0.75VDD 까지 도달하는 시간은 각각 10.7ns와 2.96ns이다.

개선된 RD 스위치를 사용할 경우 프리차징 시간 동안 BL 전압은 VDD 전압에 거의 근접함을 보여주고 있다. 모의실험 조건은 Worst Case인 VDD=1.98V, VDDP=3.0V, Temp.=-40℃, SS(Slow NMOS, Slow PMOS) 모델 파라미터를 사용하였다.

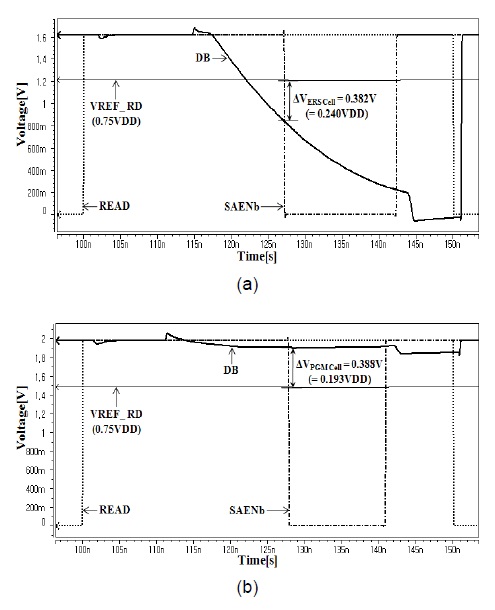

그림 8에 DB 센싱 전압과 기준전압간의 전압 차 ΔV의 모의실험 결과를 나타내었다. 그림 8(a)와 8(b)는 각각 읽기 모드에서 Erased EEPROM 셀과 Programmed EEPROM 셀의 DB 전압 파형을 나타내었다. 약 0.2VDD 이상의 Normalized ΔV 값을 가지기 위해 SAENb 신호의 지연(delay) 시간을 조절하였다. Erased 된 EEPROM 셀의 경우 최소 ΔV는 VDD=1.62V, VDDP=3.3V, Temp.=-40℃, SF(Slow NMOS, Fast PMOS) 모델 파라미터의 모의실험 조건에서 0.382V 로써 Normalized 된 값은 0.24이며 P프로그램된 EEPROM Cell의 경우 최소 ΔV는 VDD=1.98V, VDDP=3.0V, Temp.=25℃, SF 모델 파라미터 모의실험 조건에서 0.388V로써 Normalized 된 값은 0.193이다.

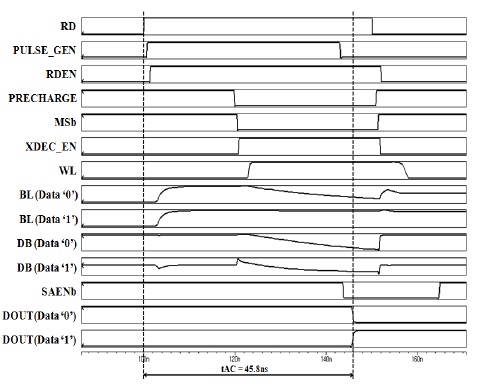

그림 9는 VDD=1.62V, VDDP=3.0V, Temp.=85℃, SS 모델 파라미터의 조건에서 읽기 모드에서의 Critical Path 모의실험 결과를 보여주고 있다. RD신호가 활성화 되면 RDEN 신호에 의해 BL이 P프리차징 된다. 이 때 DB는 대기상태 모드에서 활성화 된 PRECHARGE 신호에 의해 VDD로 프리차징 된다. PRECHARGE 신호가 Disable 되면 XDEC_EN 신호에 의해 WL이 활성화 되면서 EEPROM 셀의 데이터가 RD 스위치를 통해 DB로 전달된다. 데이터가 전달된 후 내부 지연에 의해 SAENb 신호가 활성화 되면서 DB S/A에 의해 DB의 데이터가 감지되어 DOUT 노드로 출력된다. 모의실험 결과 액세스 시간은 erased cell과 programmed cell의 경우 45.8ns로써 동일하다.

그림 10은 매그나칩반도체 0.18㎛ EEPROM 공정을 이용하여 설계된 256Kb EEPROM IP의 레이아웃 사진을 보여주고 있으며, 레이아웃 면적은 1571.625μm × 798.540μm이다.

스마트 카드와 비접촉 카드, 모바일 통신, 자동화 응용제품의 MCU등에서 실시간 정보 갱신, 보안 데이터 저장, 명령코드 저장 등의 기능을 수행하기 위해 내장형 비휘발성 메모리가 사용되고 있다. 1Mb 이하의 용량에서 주로 사용되는 EEPROM IP 시장의 설계 동향으로는 고속의 처리속도 및 높은 내구성과 낮은 전력소모 등이 요구되고 있다.

본 논문에서는 50ns의 고속 동작을 위해 기준전압을 사용하는 차동증폭기 형태의 DB 센싱 회로를 제안하여 디지털 DB 센싱 회로를 사용하였을 때 보다 DB 센싱시간을 줄였다. 또한 기존의 4개로 분리된 Distributed DB 구조를 8개로 분리하여 DB 스위칭 시간을 3.21ns 정도 줄였으며 기존의 RD 스위치 회로에서 Native 트랜지스터의 Off-leakage 전류를 줄이기 위해 사용된 5V NMOS 트랜지스터를 제거함으로써 BL의 프리차징 시간을 줄이고 DB의 센싱전압을 확보해 고속의 안정적인 동작이 가능하도록 하였다. 설계된 256Kb EEPROM IP의 액세스 시간은 45.8ns이고 매그나칩반도체 0.18μm EEPROM 공정으로 설계되었으며, 레이아웃 면적은 1571.625μm × 798.540μm이다.

![기존의 Digital DB Sensing 회로[4]](http://oak.go.kr/repository/journal/17162/HOJBC0_2015_v19n3_567_f002.jpg)

![Distirbuted DB 구조 (a) 4개로 분리된 구조[3] (b) 8개로 분리된 구조](http://oak.go.kr/repository/journal/17162/HOJBC0_2015_v19n3_567_f004.jpg)

![(a) 기존의 RD 스위치 회로[4] (b) 개선된 RD 스위치 회로](http://oak.go.kr/repository/journal/17162/HOJBC0_2015_v19n3_567_f005.jpg)