This work describes the development and comparison of two phase-locked loops (PLLs) based on a 65-nm CMOS technology. The PLLs incorporate two different topologies for the output voltage-controlled oscillator (VCO): LC cross-coupled and differential Colpitts. The measured locking ranges of the LC cross-coupled VCO-based phase-locked loop (PLL1) and the Colpitts VCO-based phase-locked loop (PLL2) are 119.84−122.61 GHz and 126.53−129.29 GHz, respectively. Th e output powers of PLL1 and PLL2 are −8.6 dBm and −10.5 dBm with DC power consumptions of 127.3 mW and 142.8 mW, respectively. The measured phase noise of PLL1 is −59.2 at 10 kHz offset and −104.5 at 10 MHz offset, and the phase noise of PLL2 is −60.9 dBc/Hz at 10 kHz offset and −104.4 dBc/Hz at 10 MHz offset. The chip sizes are 1,080 μm × 760 μm (PLL1) and 1,100 μm × 800 μm (PLL2), including the probing pads.

The increasing demand for high data rates in wireless communication systems has led to the extension of the carrier frequency up to the millimeter- and submillimeter-wave bands [1,2]. At the same time, to implement a quadrature-phase-based communication system, such as a QPSK or QAM, a local oscillator with a low phase noise is essential. Consequently, the need for a precise oscillation frequency control with a low in-band phase noise at an increased frequency has been growing, and this oscillation frequency control calls for a phase-locked loop topology (PLL) operating at the millimeter- and submillimeter-wave bands. The semiconductor technologies for this purpose have multiple options, but the Si CMOS technology is preferred in many cases because it offers a fully integrated solution with low cost, low DC power consumption, and high integration level. For this reason, recent attempts, including those by the authors [3,4], have been made to develop CMOS PLLs operating above 100 GHz. In the current work, Si CMOS PLLs operating near 120 GHz are successfully developed, and they exhibit improvement in both output power and locking range compared with the previous result [5]. The Si CMOS PLLs were achieved through a different approach taken for the voltage-controlled oscillator (VCO), a key component of high-frequency PLLs. Two types of VCOs are constructed in this work, an LC cross-coupled VCO and a differential Colpitts-based VCO. Subsequently, two PLLs based on the two VCOs, designated as PLL1 and PLL2, respectively, are developed and their performances are compared.

A PLL is a feedback system in which the frequency of a VCO output signal is divided by a divider chain, and its signal phase is controlled by comparing it with a reference signal. Fig. 1 shows the block diagram of the proposed 120 GHz PLLs. It consists of a VCO, an injection-locked frequency divider (ILFD), a 9-stage current-mode logic (CML) divider chain, a falling-edge phase frequency detector (FE-PFD), a charge pump (CP), and a second-order loop filter. The main difference between the two PLLs is the VCO structure employed inside each PLL. The description of each circuit component is as follows.

The VCO is a main component of a PLL, and it plays a critical role in high-frequency applications. The output power of the VCO determines the PLL output power level, and the locking range of the PLL is dictated by the VCO tuning range. For the PLL to be favorably used in high data rate wireless communication, the phase noise performance is critical and is affected by that of the VCO. Although the in-band phase noise of the PLL is effectively suppressed in the feedback loop, the out-band phase is still determined by the VCO phase noise.

Two VCOs are developed in this work, one with an LC cross-coupled VCO (VCO1) and the other with a differential Colpitts-based VCO (VCO2). For both VCOs, a frequency doubler is internally integrated to obtain a 2nd harmonic signal above 100 GHz for the PLL output. Compared with the case based on the fundamental-mode VCO, this harmonic approach can take advantage of a small phase noise at a low-frequency VCO operation, and it benefits the 2nd harmonic output signal of the frequency doubler. Moreover, the harmonic approach enables the fundamental signal to be taken for the frequency divider input, which saves one stage of the frequency divider chain. The schematics of the VCOs are shown in Fig. 2. The dual-mode VCOs provide the primary and secondary outputs, which correspond to the 2nd harmonic signal (2

Fig. 2(a) illustrates the schematic of VCO1. A pair of varactors with a size of 0.25 μm × 6 μm is integrated with the VCO core to control the oscillation frequency, and source-follower buffers (M3, M4) are connected for the fundamental output signal (

The simulated oscillation frequency, output power, and phase noise of the VCOs are plotted in Fig. 3. As shown in Fig. 3(a), the simulated oscillation frequency (2

Among various topology options for frequency dividers, ILFDs have recently emerged as a viable option for millimeter-wave applications because of their high operation frequency with reasonable power consumption. As the frequency of the signal injected into the divider chain in the PLL in this work is high at around 60 GHz, an ILFD is adopted for the first stage of the frequency divider chain. Fig. 4 is the circuit schematic of the V-band ILFD used in this study. The frequency alignment with the VCO is a key issue because of the narrow locking range of the ILFD at high frequency. Therefore, an LC cross-coupled oscillator-based ILFD, which has a similar structure as the VCO and is suitable for frequency alignment, is adopted. A pair of varactors is integrated with the circuit core to enable the tuning of the locking frequency. The oscillator core embedded in the divider oscillates near the half (near 30 GHz) of the input signal, which is injected into the common source node of

The remaining part of the frequency divider chain is implemented with a 9-stage divide-by-two CML divider, which has a division ratio of 512. Thus, the total division ratio of the divider chain is 1024, decreasing the fundamental frequency

The two PLLs were fabricated using the Samsung 65-nm 1P8M CMOS technology, which exhibits

First, the individual VCOs were characterized, and the results were described. Fig. 6 shows the setups for measuring the frequency spectrum and the output power of the two VCOs. The output spectrum of each VCO was measured by an Agilent E4407B spectrum analyzer after a frequency down-conversion with a QuinStar D-band subharmonic mixer, in which an on-chip probing was employed with a GGB D-band (110–170 GHz) waveguide probe (Fig. 6(a)). An Agilent 50-75 GHz signal source module, which multiplies the signal from a Keysight E8257D signal generator, served as the local oscillator for the down-conversion. The output power was measured through an Erikson PM4 power meter without a frequency down-conversion (Fig. 6(b)). The measured tuning range and the output power variation of the VCOs are shown in Fig. 7. With

Second, the ILFD was characterized for the input sensitivity and the locking range. The input signal (

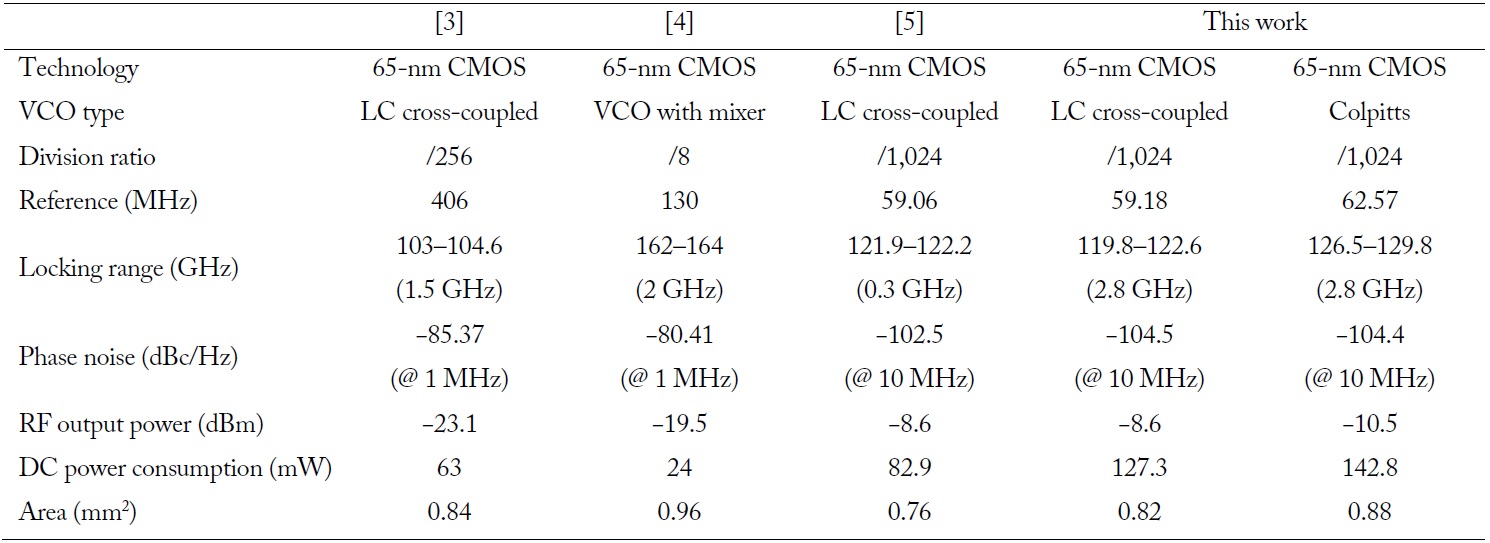

Finally, the integrated PLLs were characterized. The PLL measurement setup was similar to that of the VCOs, in which the 2nd harmonic output signal was down-converted and measured by the same spectrum analyzer. One difference from the VCO test setup is the injection of the reference signal near 60 MHz into the FE-PFD; this signal is generated by an Agilent E8247C signal generator. Fig. 9 shows the measured output spectra of the fabricated PLLs. The measured locking range of PLL1 was 119.84–122.61 GHz and that of PLL2 was 126.53–129.27 GHz, and they were included in the entire tuning range of the associated VCOs. In the spectrum, reference spurs at around 60 MHz were observed on both sides of the center frequency; this outcome could be considered evidence of the locked state. Fig. 10 shows the measured phase noise plot of the PLLs in the locked state. The phase noise of PLL1 was measured as −59.2 at 10 kHz offset and −104.5 at 10 MHz offset. For PLL2, −60.9 dBc/Hz and −104.4 dBc/Hz were obtained for 10 kHz and 10 MHz offsets, respectively. Deducing that the phase noise performance shows little difference is reasonable. Both plots show reference spurs at the same frequency offset as that observed in the output spectrum in Fig. 9. The measured output powers were −8.6 dBm and −10.5 dBm for PLL1 and PLL2, respectively, at around the operation frequency. The total DC power consumptions were 127.3 mW for PLL1 and 142.8 mW for PLL2. In terms of the output power and the DC-to-RF efficiency, PLL1 performed slightly better than PLL2. Table 1 summarizes the performance of the PLLs based on the 65-nm CMOS technology operating above 100 GHz.

[Table 1.] Comparison of the CMOS PLLs operating over 100 GHz

Comparison of the CMOS PLLs operating over 100 GHz

Two PLLs based on the 65-nm CMOS technology operating near 120 GHz are developed. Each PLL adopts a different VCO topology, either the LC cross-coupled or the Colpitts, and the measured performances are compared. This work not only demonstrates the feasibility of implementing the PLLs over 100 GHz based on the CMOS technology but also compares the two popular topologies for the VCOs incorporated into the PLLs. The developed PLLs can be adopted as a stable signal source for various applications beyond 100 GHz, including D-band communication systems.