본 연구에서는 비대칭 이중게이트 MOSFET의 채널길이와 채널두께의 비에 따른 문턱전압이하 스윙의 변화를 분석하고자한다. 비대칭 이중게이트 MOSFET는 상하단 게이트 구조를 달리 제작할 수 있어 단채널효과를 제어할 수 있는 요소가 증가한다는 장점이 있다. 특히 채널길이를 감소하였을 경우 문턱전압이하 스윙의 급격한 증가로 인한 특성저하 현상을 감소시킬 수 있다. 그러나 스켈링 이론에 따라 채널길이 감소에 따라 채널두께도 변화되어야하며 이에 문턱전압이하 스윙이 변화하게 된다. 그러므로 채널길이와 채널두께의 비가 문턱전압이하 스윙을 결정하는 중요 요소가 된다. 해석학적으로 문턱전압이하 스윙을 분석하기 위하여 해석학적 전위분포를 포아송방정식을 통하여 유도하였으며 다양한 채널길이 및 채널두께에 대하여 전도중심과 문턱전압이하 스윙을 계산한 결과 채널길이와 채널두께의 비에 따라 전도중심과 문턱전압이하 스윙이 변화한다는 것을 알 수 있었다.

This paper has analyzed the variation of subthreshold swing for the ratio of channel length and thickness for asymmetric double gate MOSFET. The asymmetric double gate MOSFET has the advantage that the factors to control the short channel effects increase since top and bottom gate structure can be fabricated differently. The degradation of transport property due to rapid increase of subthreshold swing can be specially reduced in the case of reduction of channel length. However, channel thickness has to be reduced for decrease of channel length from scaling theory. The ratio of channel length vs. thickness becomes the most important factor to determine subthreshold swing. To analyze hermeneutically subthreshold swing, the analytical potential distribution is derived from Poisson’s equation, and conduction path and subthreshold swing are calculated for various channel length and thickness. As a result, we know conduction path and subthreshold swing are changed for the ratio of channel length vs. thickness.

다중게이트 MOSFET(Multi Gate MOSFET; MugFET) 소자는 기존 CMOSFET의 초미세화시 발생하는 단채널 효과를 최소화하기 위하여 개발된 소자이다.[1,2]. MugFET는 채널주위에 2개 이상의 게이트를 제작하여 게이트 전압에 의한 채널 내 반송자의 제어능력을 향상시키는 소자이다. 여러 종류의MugFET가 개발되고 있지만 대표적인 소자로는 이중게이트(Double Gate; DG) MOSFET[3,4]와 FinFET[5,6]가 있다. FinFET는 채널을 지느러미(Fin)형태의 얇고 높은 형태로 제작하고 그 주위를 게이트 단자로 감싸준 형태로 이루어진 소자로 지느러미 형태의 채널을 제작하는데 어려움을 겪고 있다. DGMOSFET는 상단과 하단에 게이트를 제작하여 채널 내 전류 제어능력을 약 2배 정도 향상시킨 소자로서 대칭형과 비대칭형으로 나누어진다. 대칭형은 상단과 하단의 게이트 산화막 두께가 동일하고 인가된 게이트 전압도 동일하게 제작한다. 그러나 비대칭형 DGMOSFET는 상단과 하단의 게이트 산화막 두께를 각각 달리 제작할 수 있을 뿐만 아니라 상하단의 게이트 전압을 달리 인가할 수 있다. 그러므로 비대칭형 DGMOSFET는 단채널효과를 제어할 수 있는 설계 파라미터가 증가하여 효율적으로 단채널효과를 제어할 수 있다. 단채널효과 중 문턱전압이하 스윙값의 저하는 트랜지스터가 초소형화될 때 발생하는 2차 효과로써 디지털응용에 제한을 가하며 특히 차단전류의 증가를 야기하여 집적도 향상에 걸림돌이 되고 있다.

이에 본 연구에서는 비대칭 DGMOSFET의 문턱전압이하 스윙을 채널길이 및 채널두께의 비에 따라 분석할 것이다. 채널의 크기를 결정하는 채널의 길이와 두께는 DGMOSFET의 전송특성을 결정하는 가장 중요한 요소이다. 스켈링 이론에 따라 채널길이와 채널두께는 비례하여 변화하고 있지만 DGMOSFET의 특성상 일반적인 스켈링 이론이 성립하지 않을 것이다. 그러므로 채널길이와 채널두께를 다양하게 변화시켰을 경우, 그 비에 따라 문턱전압이하 스윙 값의 감소 및 증가 등을 관찰함으로써 채널길이와 채널두께의 최적의 비를 관찰하고자 한다.

문턱전압이하 스윙 모델을 제시하기 위하여 비대칭 DGMOSFET의 채널 내 해석학적 전위분포를 포아송방정식을 이용하여 구하였으며 이때 전하분포는 Ding 등의 모델[7]과 달리 가우스 분포함수를 이용하였다. 이와 같이 구한 문턱전압이하 모델의 타당성을 2차원 수치해석학적 모델과 비교하여 타당성을 입증하였으며 이 모델을 이용하여 채널길이와 채널두께의 비에 따라 문턱전압이하 스윙값 및 전도중심의 변화를 관찰하고 결과를 고찰하였다.

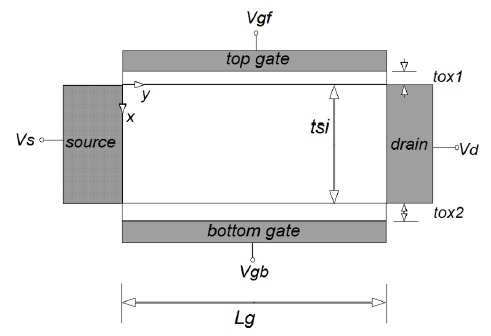

그림 1은 비대칭 DGMOSFET의 개략도이다. 그림에서 알 수 있듯이 상단과 하단의 게이트 전압을 달리 인가할 수 있으며 산화막 두께 또한 상단과 하단을 각각 달리 지정할 수 있어 설계 파라미터가 증가하게 된다. 즉, 비대칭 DGMOSFET는 상단과 하단 게이트의 역할을 구분함으로써 전류제어 능력을 향상시키고자 개발된 소자이다. Ding 등[7]은 일정한 채널도핑농도 분포함수를 이용하여 비대칭 DGMOSFET의 표면전위 및 문턱전압이하 스윙특성을 해석하였다.

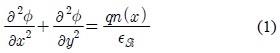

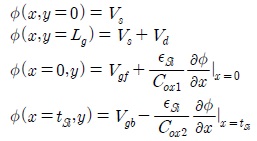

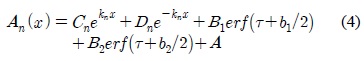

그러나 도핑을 위하여 광범위하게 사용되는 기술인 이온주입법의 경우, 도핑분포는 가우스분포함수를 따르므로 본 연구에서는 전하분포함수를 가우스분포함수로 사용하였다. 먼저 그림 1의 채널 내 전위분포를 구하기 위하여 식(2)의 도핑분포함수를 이용하여 식 (1)의 2차원 포아송방정식을 풀어 해석학적 전위분포를 구하였다.

여기서

여기서

이며 여기서

이때 상단 게이트 전압

이다.

문턱전압이하 스윙을 구하기 위하여 식 (5)의

여기서

식 (5)의 문턱전압이하 스윙 모델은 채널길이

Ⅲ. 소자 파라미터에 따른 문턱전압이하 스윙 결과 고찰

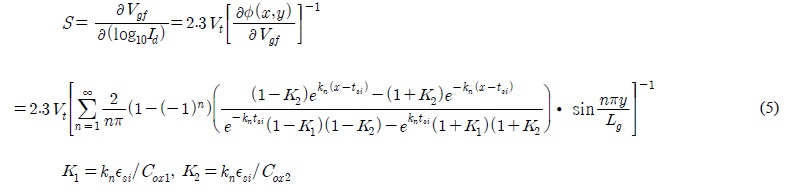

본 연구의 문턱전압이하 스윙 모델에 대한 타당성을 입증하기 위하여 시뮬레이션 조건을 채널길이 30 nm, 채널두께 10 nm, 도핑농도 1016/㎤로 하였을 경우 채널두께를 25 nm, 20 nm, 15 nm로 변화시키면서 채널길이에 따라 문턱전압이하 스윙값을 구하여 2차원 수치해석학적 시뮬레이션인 Medici의 결과[7]와 그림 2에서 비교하였다. 그림 2에서 알 수 있듯이 본 연구에서 제시한 식 (5)의 결과는 2차원 수치해석학적 해와 잘 일치하는 것을 알 수 있다. 그러므로 본 연구에서 제시한 문턱 전압이하 스윙에 대한 모델 식(5)는 타당하다고 사료된다. 그림 2에서 알 수 있듯이 채널길이가 증가할수록 그리고 채널두께가 감소할수록 문턱전압이하 스윙은 감소한다. 그러나 감소정도는 선형적인 관계는 아니므로 채널길이와 두께의 비에 따라 문턱전압이하 스윙 및 전도중심의 관계를 관찰할 것이다.

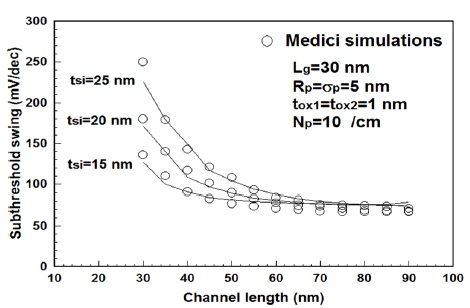

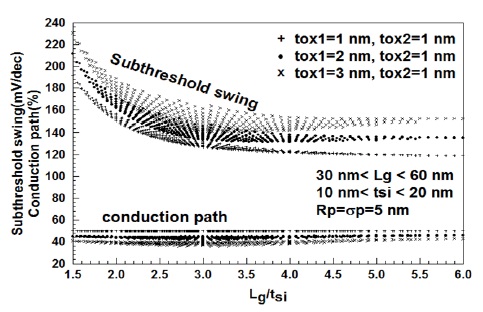

그림 3에 채널길이를 30 nm에서 60 nm까지 그리고 채널두께를 10 nm에서 20 nm까지 변화시키면서 하단 산화막 두께 변화에 따른 문턱전압이하 스윙값 변화를 도시하였다.

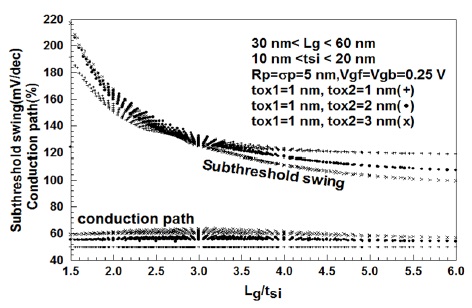

그림 3과 모든 조건은 동일하게 유지하면서 단지 파라미터를 상단게이트 산화막 두께로 변화시켜 문턱전압 이하 스윙의 변화를 그림 4에 도시하였다. 그림 3과 비교해보면

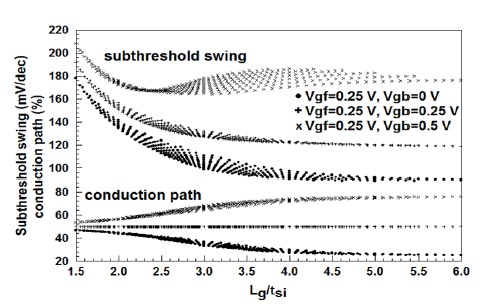

비대칭 이중게이트 MOSFET는 상단과 하단의 게이트 산화막을 달리 제작할 수 있을 뿐만 아니라 상단과 하단의 게이트 전압을 달리 인가할 수 있다. 상단과 하단 게이트 전압의 영향을 고찰하기 위하여 그림 3과 모든 조건을 동일하게 유지하면서 하단 게이트 전압을 파라미터로 하여

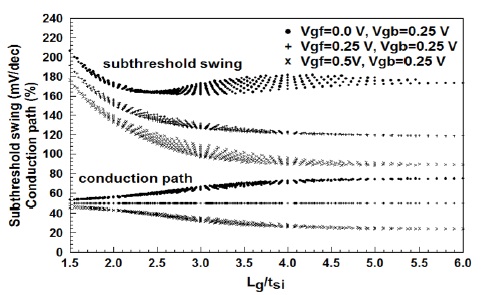

상단 게이트전압을 파라미터로 하여 그림 5와 같이 문턱전압이하 스윙을

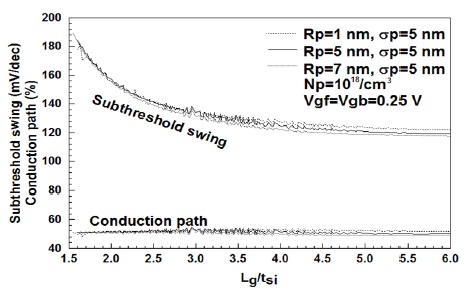

본 연구에서는 비대칭 이중게이트 MOSFET의 채널길이와 채널두께의 비에 따른 문턱전압이하 스윙의 변화를 산화막 두께, 게이트 전압 그리고 도핑분포함수 등에 따라 분석하였다. 본 연구에서 제시한 문턱전압이하 스윙모델이 이차원 수치해석학적 해와 잘 일치하므로 모델의 타당성이 입증되었으며 문턱전압이하 스윙과 전도중심의 변화를 관찰하였다. 관찰한 결과