COMS(Communication, Ocean and Meteorological Satellite), the first Korean geostationary meteorological satellite, provides free meteorological information through HRIT/LRIT(High/Low Rate Information Transmission) service. This work presents the development of data receiver circuit that is essential to the implementation of a low-cost meteorological information receiver system. The data receiver circuit processes the data units according to the specification of physical layer and data link layer of HRIT/LRIT service. For this purpose, the circuit consists of a Viterbi decoder, a sync. word detector, a derandomizer, a Reed-Solomon decoder and so on. The circuit also supports PCI express interface to pass the information data on to the host PC. The circuit was implemented on an FPGA(field programmable gate array) and its function was verified through simulations and hardware implementation.

천리안 위성(COMS: Communication, Ocean and Meteorological Satellite)은 우리나라 최초의 정지궤도 복합위성으로 기상 관측, 해양 관측 그리고 통신서비스 임무를 수행한다. 천리안 위성의 독자적인 운영을 통해 최대 8분 간격으로 한반도 부근 지역을 관측·감시할 수 있게 되었고 위험 기상 발생 시 우리나라 영역 중심으로 독자적인 관측 영역 설정 및 관측 시각 조정이 가능하게 되었다. 그리고 이를 통해 독자적인 기상 자료처리 시스템 운영과 수치 예보 지원을 위한 자료 생산이 가능하게 되었다[1,2].

천리안 위성에서 생산된 영상자료와 산출물은 수치예보자료, 해양관측자료 등 여러 자료와 함께 국제규격의 위성 자료 형식인 HRIT/LRIT 형태로 변환되어 중·소규모 수신 시스템 사용자에게 무료로 제공되고 있다. 그림 1은 천리안 위성으로부터 수신할 수 있는 기상 정보의 한 예인 적외영상을 보여준다[2].

천리안 위성의 기상정보를 수신하기 위해서는 고가이면서 복잡한 장비가 필요하다. 이것은 기상정보의 직접 활용을 위해 자체적으로 기상정보 수신처리 시스템을 갖추고자 하는 사용자에게 큰 부담이 될 수 있으며 기상정보의 민간 활용이나 활용 저변 확대에 가장 큰 걸림돌이다. 스마트 디바이스의 보급과 사물인터넷(IoT) 기술의 개발에 따라 앞으로 기상정보의 접근성에 대한 요구도 증가할 것으로 보인다. 이를 만족하기 위해서는 간단하며 구축비용이 적은 보급형 위성 기상정보 수신처리 시스템이 필요하다.

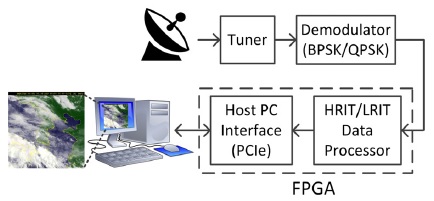

본 논문은 보급형 위성 기상정보 수신처리 시스템에 적용할 수 있는 기상정보 데이터 수신회로 개발에 대해 소개한다. 그림 2는 개발된 기상정보 데이터 수신회로가 적용될 개인용 PC 기반의 보급형 천리안위성 기상정보 수신시스템의 구성을 보여준다. 안테나에서 수신된 기상정보는 튜너와 복조기를 거쳐 FPGA로 구현되는 기상정보 데이터 수신회로로 공급된다. 본 논문에서 소개되는 기상정보 데이터 수신회로는 HRIT/LRIT 서비스의 물리 계층(physical layer)과 데이터 링크 계층(data link layer)에 대응하는 작업을 수행하는 HRIT/LRIT 데이터 처리회로와 기상정보를 PCIe(PCI Express) 방식[3]으로 사용자 PC에 전달하는 호스트 PC 인터페이스 회로로 이루어진다.

천리안 위성은 관측된 기상 자료를 복사 보정과 기하보정을 거친 후 생성된 기상 영상 파일을 HRIT 서비스와 LRIT 서비스, 두 가지 형태로 제공하고 있다. HRIT 서비스는 중규모수신 시스템을 위한 서비스이며 LRIT 서비스는 소규모수신 시스템을 위한 서비스이다. HRIT/LRIT 서비스는 각각 표준 기술서 [4]와 [5]의 내용을 따른다. 표준 기술서 [4]와 [5]는 CCSDS(The Consultative Committee for Space Data Systems)[6]에서 제안하는[7]을 바탕으로 하여 CGMS(the Coordination Group for Meteorological Satellites)에서 규정한 [8]을 기반으로 작성되었다.

표준 기술서 [4]와 [5]에는 천리안 위성으로부터 전송되는 HRIT/LRIT 데이터에 대해 OSI(Open Systems Interconnection)의 각 계층에 대응하는 형식이 정의되어 있다. 본 논문에서 소개되는 천리안위상 기상정보 수신처리부는 데이터 링크 계층의 일부와 물리 계층의 일부를 처리하므로 이 절에서는 HRIT/LRIT 서비스의 데이터 링크 계층과 물리 계층에 대해 간략히 설명한다. HRIT/LRIT 서비스의 데이터 링크 계층은 크게 VCLC(virtual channel link control) 부계층(sub-layer)과 VCA(virtual channel access) 부계층으로 나뉜다.

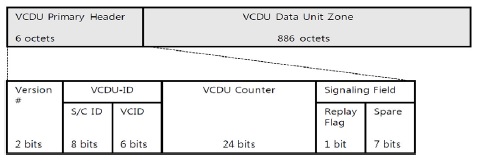

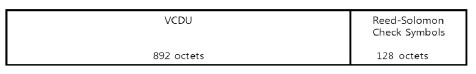

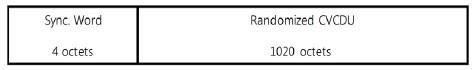

VCLC 부계층은 네트워크 계층으로부터 전달되는 VCID(virtual channel ID)를 기반으로 하는 다중 서비스를 제공하며 네트워크 계층으로부터 전달되는 다수의 M_SDU(multiplexing service data unit)를 이용해 M_PDU(multiplexing protocol data units)를 구성한다. VCA(virtual channel access) 부계층에서는 헤더와 M_PDU를 결합하여 그림 3과 같은 VCDU(virtual channel data units)가 만들어지며 VCDU에 (255/223, 4) Reed-Solomon 인코딩[9]를 적용한 그림 4와 같은 CVCDU(coded virtual channel data unit)가 만들어진다.

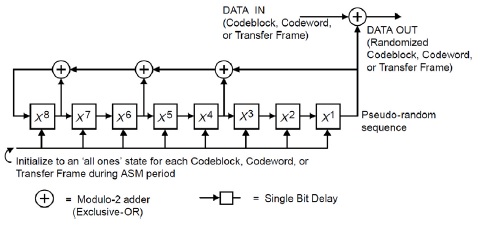

CVCDU에 다항식

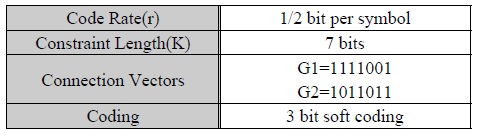

물리 계층에서는 데이터 링크 계층에서 전달된 CADU에 (r=1/2, K=7) 컨볼루션 코딩(Convolution coding)[9,10]이 적용되고 그 결과가 HRIT 서비스에서는 QPSK(quadrature phase shift keying) 방식으로 LRIT 서비스에서는 BPSK(binary phase shift keying) 방식으로 변조되어 전송된다.

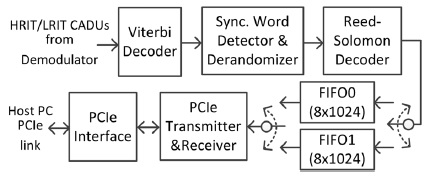

기상정보 데이터 수신회로는 그림 6과 같이 컨볼루션 코딩에 대응하는 디코딩을 수행하는 Viterbi 디코더[9,10], 프레임 동기 검출을 위한 Sync. word 감지회로와 PN 코드를 적용 효과를 없애기 위한 Derandomizer, Reed-Solomon 인코딩에 대응하는 디코딩을 수행하는 Reed-Solomon 디코더, 송신용 FIFO, PCIe 송수신회로, PCIe 인터페이스 회로로 구성된다.

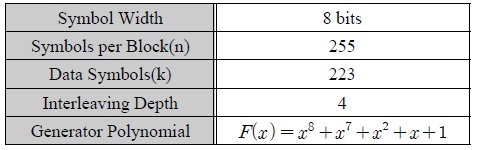

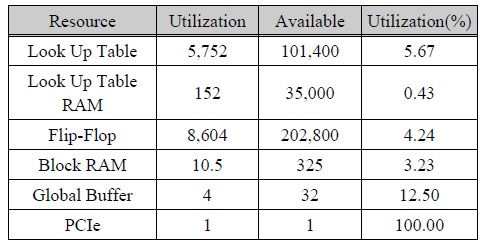

복조기로부터 공급되는 CADU는 AXI4-Stream 인터페이스[11]을 통하여 Viterbi 디코더에 공급된다. Viterbi 디코더의 동작 사양은 표 1과 같다.

Viterbi 디코더의 사양

Viterbi 디코더를 통과한 CADU는 특정 비트열 ‘1ACFFCIDh’을 감지하는 Sync. word 감지회로에 의해 그 시작이 검출되며 이 후에 수신되는 CVCDU는 그림 7과 같은 구조를 갖는 Derandomizer를 통과하여 PN 코드의 영향이 제거된다.

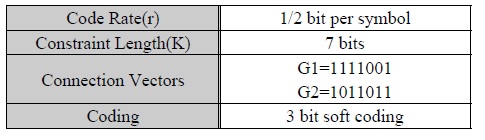

CVCDU는 AXI4-Stream 인터페이스를 통하여 Reed-Solomon 디코더에 공급되어 전송과정에 발생한 오류가 정정되고 VCDU가 얻어진다. Reed-Solomon 디코더에는 4 채널 심볼 인터리빙(Symbol interleaving)이 적용되며 그 사양은 표 2와 같다. 수신된 VCDU들은 PCIe 송수신회로에 의해 호스트 PC로 전송될 수 있도록 두개의 송신용 FIFO에 AXI4-Stream 인터페이스를 통하여 저장된다. 각 송신용 FIFO는 한 개의 VCDU를 저장할 수 있으며 두 개의 송신용 FIFO가 교대로 사용된다. VCDU가 송신용 FIFO에 저장될 때마다 PCIe 송수신회로에 의해 PCIe 인터페이스 회로를 통하여 호스트 PC로 전송된다.

Reed-Solomon 디코더의 사양

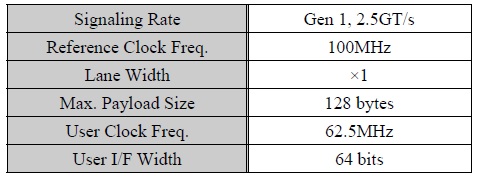

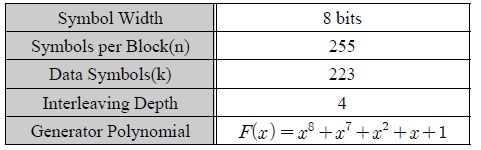

PCIe 인터페이스 회로는 PCIe 2.1 사양을 만족하는 Endpoint[3] 역할을 수행한다. PCIe 2.1 사양은 일반적으로 PC측에 위치하는 Root Complex와 PC의 PCIe 슬롯에 장착되는 카드에 위치하는 Endpoint 사이의 직렬 통신 방식 데이터 교환을 위한 트랜잭션 계층(Transaction Layer), 데이터 링크 계층, 물리 계층을 규정하고 있다. PCIe 인터페이스 회로의 PCIe 2.1관련 주요 사양은 표 3과 같다.

PCIe 인터페이스 회로 사양

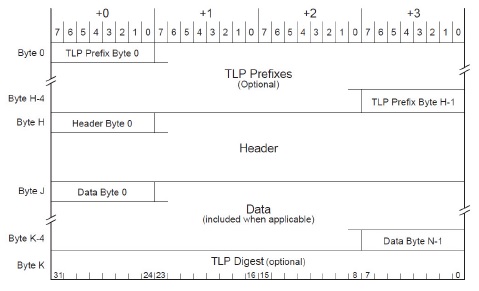

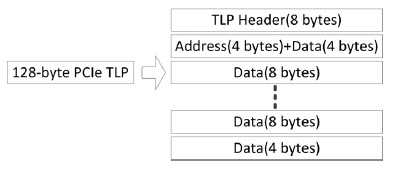

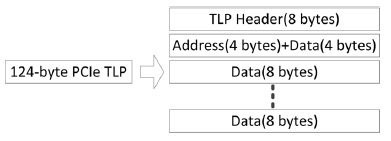

가장 상위 계층인 트랙잭션 계층에서는 그림 8과 같은 TLP(Transaction Layer Packet)를 이용하여 데이터가 교환된다. PCIe 인터페이스 회로는 PCIe 송수신회로로부터 전달 받은 VCDU를 메모리 쓰기 요청(Memory Write Request) TLP로 변환하여 호스트 PC의 Root Complex에 전달한다. 그리고 호스트 PC의 Root Complex로부터 전달되는 메모리 읽기/쓰기 요청(Memory Read/Write Request) TLP를 PCIe 송수신회로에 전달하기도 한다.

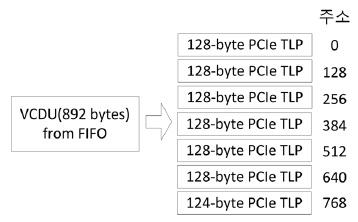

PCIe 송수신 회로는 PCIe 인터페이스 회로를 통하여 호스트 PC로부터 TLP 형태로 전달되는 명령을 해독하여 내부 동작 관련 설정을 변경하거나 내부 동작 상태를 호스트 PC로 반환한다. 그리고 호스트 PC의 명령에 의해 FIFO에 저장되어 있는 VCDU를 분할하여 AXI4-Stream 인터페이스를 통하여 PCIe 인터페이스 회로에 전달한다. 이를 위해 총 3 개의 FSM(Finte Sate Machine)이 유기적으로 결합되어 동작하며 그림 9처럼 892 바이트 크기를 갖는 VCDU를 데이터 크기가 128 바이트인 6개의 TLP와 데이터 크기가 124 바이트인 한 개의 TLP로 변환하여 PCIe 인터페이스 회로에 전달한다. 이 과정에서 7개의 TLP를 수신한 호스트 PC측에서 VCDU를 복원할 수 있도록 TLP마다 특정 주소값이 할당된다.

PCIe 인터페이스 회로는 64 비트 AXI4-Stream 인터페이스를 이용하기 때문에 128 바이트 TLP와 124 바이트 TLP는 각각 그림 10과 11처럼 TLP 헤더, 주소, 데이터의 순서로 PCIe 송수신 회로에 의해 PCIe 인터페이스 회로로 전달된다.

기상정보 데이터 수신회로를 구현할 FPGA는 성능, 향후 확장성과 가격대를 고려하여 Xilinx사의 Kintex-7계열 중 하나인 XC7K160TFBG676-1[12]가 채택되었다. 그리고 개발을 위한 EDA(Electronic Design Automation) 도구는 Xilinx사의 Vivado Design Suite[12]가 채택되었다. 효율적 개발을 위해 Viterbi 디코더, Reed-Solomon 디코더, PCIe 인터페이스 회로는 Vivado Design Suite에서 제공되는 IP(Intellectual Property)를 활용하였으며 나머지 부분은 VHDL언어로 개발되었다.

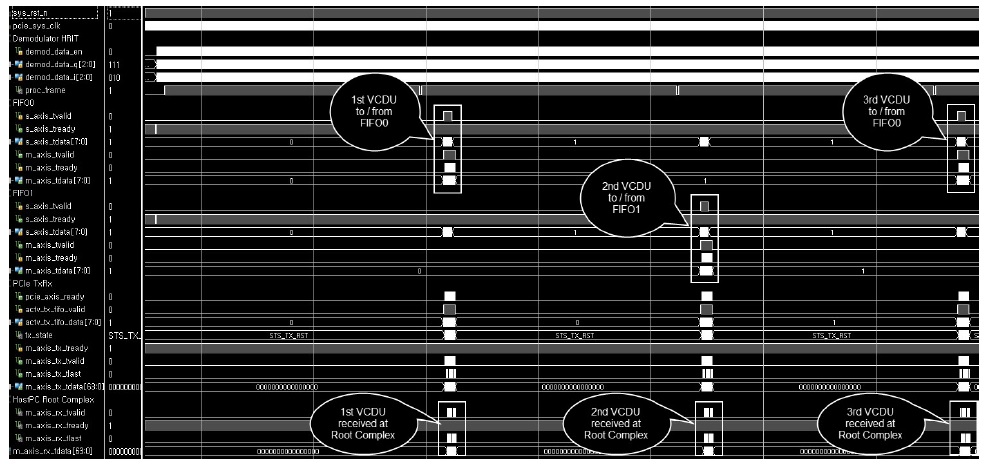

그림 12는 복조기로부터 공급된 3개의 CADU로부터 VCDU가 추출되어 두 개의 FIFO에 교대로 저장되고 PCIe 송수신 회로와 PCIe 인터페이스 회로를 통해서 호스트 PC의 Root Complex에 수신되는 상황을 시뮬레이션한 것이다. 실제 천리안 위성의 기상정보 데이터를 활용하여 작성된 테스트 벤치가 사용되었고 호스트 PC에 기상정보가 정상적으로 수신되는 시뮬레이션 결과를 확인하였다.

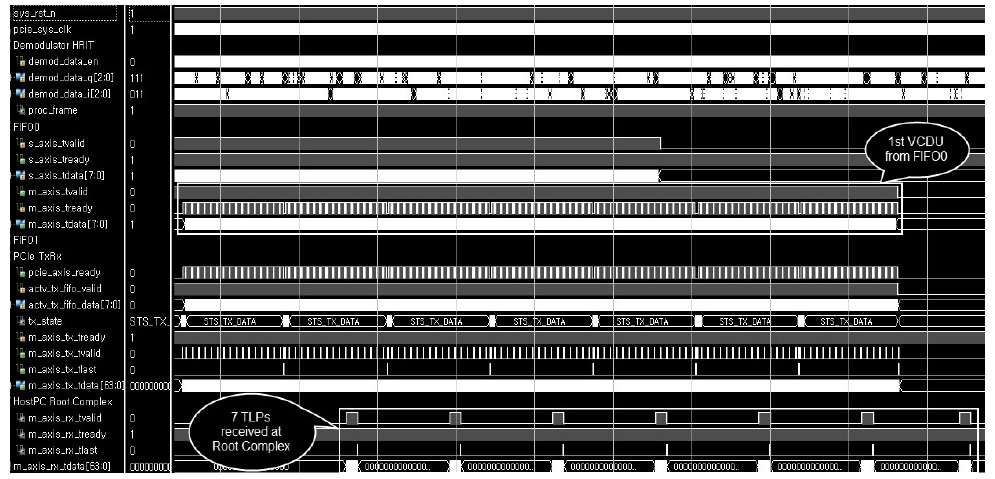

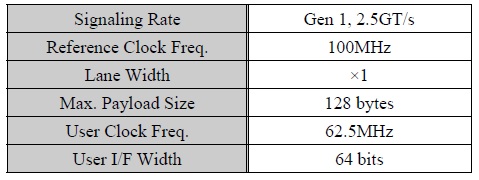

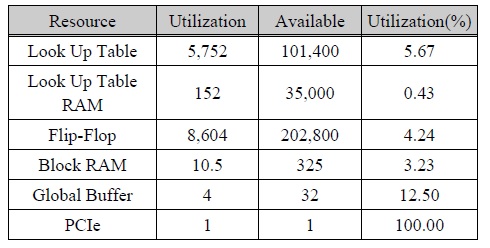

그림 13은 그림 12의 시뮬레이션 중 첫 번째 수신된 VCDU가 7개의 TLP 형태로 호스트 PC의 Root Complex에 수신되는 시뮬레이션 파형을 보여준다. 그리고 표 4는 개발된 회로의 FPGA 자원 사용률을 보여준다. 채택된 FPGA보다 훨씬 저렴한 가격의 FPGA로도 구현될 가능성이 매우 높다는 것을 알 수 있다.

FPGA 자원 사용률

그림 14는 기상정보 데이터 수신회로가 FPGA로 구현된 기상정보 데이터 수신카드(㈜휴미디어[13])를 보여준다. 수신카드는 FPGA, 튜너, 복조회로 그리고 기타회로들을 포함하며 호스트 PC의 PCIe 슬롯에 장착될 수 있다. 기상정보 데이터 수신회로를 그림 14의 수신카드의 FPGA에 구현하고 그림 15의 시험 환경을 이용하여 기상정보 데이터 수신회로가 설계 의도대로 동작하는 것을 확인하였다.

본 논문에서는 개인용 PC 기반의 보급형 천리안 위성 기상정보 수신시스템 구현을 위해 개발된 FPGA 기반 기상정보 데이터 수신회로를 소개하였다. 개발된 기상정보 데이터 수신회로는 복조기로부터 공급되는 천리안 위성의 HRIT/LRIT 서비스 데이터 유닛에 대해 물리계층과 데이터 링크 계층에 대응하는 작업을 수행하여 호스트 PC에서 실행되는 기상정보 처리 소프트웨어가 처리할 수 있도록 기상정보 데이터를 공급하여준다.

이를 위해 Viterbi 디코더, Sync. word 감지회로, Derandomizer, Reed-Solomon 디코더를 포함하며 호스트 PC로의 고속 데이터 전송을 위해 채택된 PCIe 방식에 대응하기 위해 PCIe 인터페이스 회로와 이를 제어하기 위한 PCIe 송수신회로를 포함한다. 개발된 기상정보 데이터 수신회로는 Xilinx사의 Kintex-7 계열 FPGA에 실제 구현되어 그 기능이 검증되었으며 관련 기능이 보완되면 향후 발사되어 운영될 예정인 정지궤도 복합위성 2A(GEO KOMPSAT-2A)이 제공하는 UHRIT(Ultra HRIT) 서비스에 대응하는 기상정보 수신시스템에도 활용될 수 있다.