전류컨베이어 회로를 이용한 주파수 고정 루프 회로를 0.35㎛ CMOS 공정으로 설계하였다. 공급전압은 3volts를 사용하였다. 설계된 회로는 분주기, 주파수-전압 변환기, 전압 감산기 및 발진기로 구성하였으며, 각 회로 블록을 대 칭적으로 배치하여 공정 변화에 따른 신뢰성 특성을 향상시켰다. HPICE 시뮬레이션 결과 MOS 트랜지스터의 채널 길이, 채널 폭, 저항 및 커패시터의 크기가 ±5% 변화할 때 출력주파수의 변화율은 ±1% 내외였다.

In this paper, the FLL(Frequency Locked Loop) circuit using current conveyor circuit is designed by 0.35㎛ CMOS process. The FLL circuit is built in a frequency divider, a frequency-to-voltage converter, a voltage subtractor and a oscillator and the circuit blocks have a symmetric structure to improve a reliability characteristics with a process variation. From the simulation results, the variation rate of output frequency is about less than ±1% when the channel length, channel width, resistance and capacitance are varied ±5%.

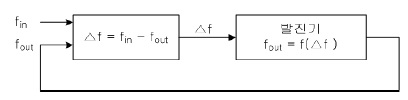

입력 신호의 주파수를 추적하는 다양한 형태의 주파수 고정 루프 회로가 연구되어 지고 있다. 주파수 고정루프 회로는 위상 고정 루프 회로와 동작은 유사하나 위상 고정 루프 회로에 비해 비교적 간단하게 구성할 수 있다. 주파수 고정 루프 회로의 기본적인 구성은 그림 1과 같다. 입력신호의 주파수와 출력신호의 주파수를 비교하여 주파수 차이에 비례하는 신호, △f를 생성한다. 생성된 신호는 발진기의 출력주파수를 제어하여 입력신호의 주파수와 출력 신호의 주파수가 동일한 값이 되도록 한다.

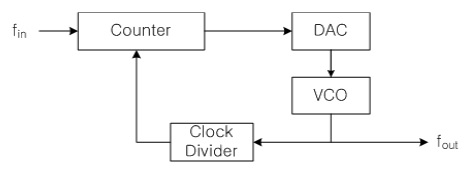

그림 2는 카운터를 이용한 주파수 고정 루프회로 블록도로서, 카운터를 이용하여 일정 시간동안 입력 펄스의 수를 헤아린다. 그리고 카운터 값을 디지털-아날로그 변환기(Digital-Analog Converter)를 통하여 아날로그 전압으로 변환한 다음, 전압제어발진기(Voltage-Controlled Oscillator)를 이용하여 출력주파수를 생성한다[2-4].

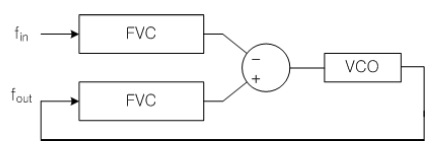

그림 3은 주파수-전압 변환기를 사용한 고정 루프회로 블록도로서 주파수-전압 변환기(Frequency Voltage Converter)를 이용하여 입력주파수(fin)와 출력주파수(fout)에 비례하는 전압을 생성한 다음, 두 전압의 차이를 구한다. 그리고 두 전압의 차이를 전압제어발진기의 입력신호로 사용하여 출력주파수를 생성하는 것이다[1,5,6].

그림 2와 그림 3과 같이 주파수 고정 루프 회로는 설계 방법에 따라 다소의 차이는 있겠지만, 일반적으로 아날로그 회로 블록과 디지털 회로 블록으로 구성된다[1,2]. 설계된 회로를 집적화할 때, 포토 리소그래피를 이용한 게이트 및 소스/드레인 패턴 형성, 에칭 그리고 소스/드레인의 불순물 확산 등 반도체 제조 공정의 진행에 따라 MOS(Metal Oxide Semiconductor) 트랜지스터의 채널 길이 및 폭은 설계된 크기에 비해 증가하거나 감소한다. 이와 같이 채널 길이와 폭의 변화는 MOS 트랜지스터의 전기적인 특성을 변화시키고, 이로 인해 회로의 출력 특성은 변화된다. 그림 1의 경우 MOS 트랜지스터의 전기적인 특성이 변화하면 동일한 입력신호에 대해서 △f 값이 변화되고, 이로 인해 출력주파수 fout이 변화된다. 본 논문에서는 각 회로 블록을 대칭적으로 레이아웃 할 수 있도록 설계하여 MOS 트랜지스터의 특성 변화로 인한 영향이 상쇄되도록 하여 회로의 신뢰성 특성을 향상시킬 수 있도록 설계하고자 한다.

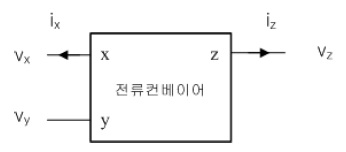

그림 4는 주파수 고정 루프회로에 사용된 전류 컨베이어 회로의 블록도이다. 전류 컨베이어 회로는 입력 단자와 출력 단자의 전류 방향에 따라 양의 극성 혹은 음의 극성을 가진 두 종류가 있다. 양의 극성을 가지는 전류 컨베이어 회로에서 출력전류의 방향과 크기는 입력전류와 동일하며, 음의 극성을 가지는 전류 컨베이어회로에서는 출력전류의 크기는 입력 전류와 동일하지만, 방향은 반대 방향으로 흐른다.

양의 극성을 가지는 전류 컨베이어 회로의 특성은 식 (1), (2), (3)과 같다[6].

여기서

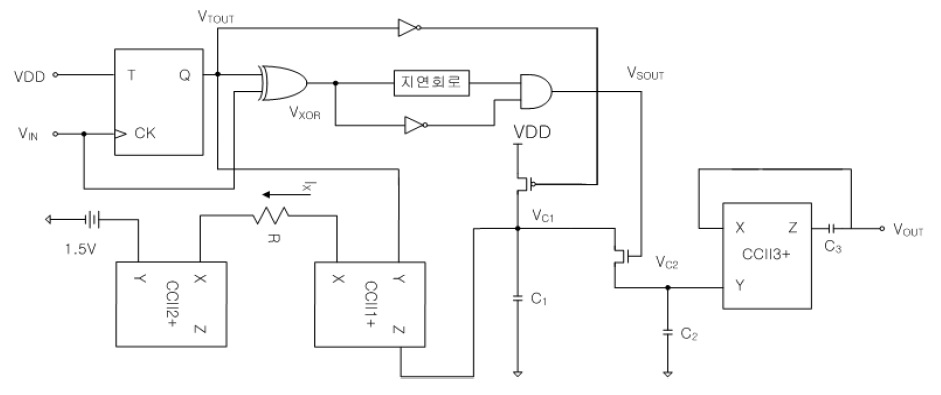

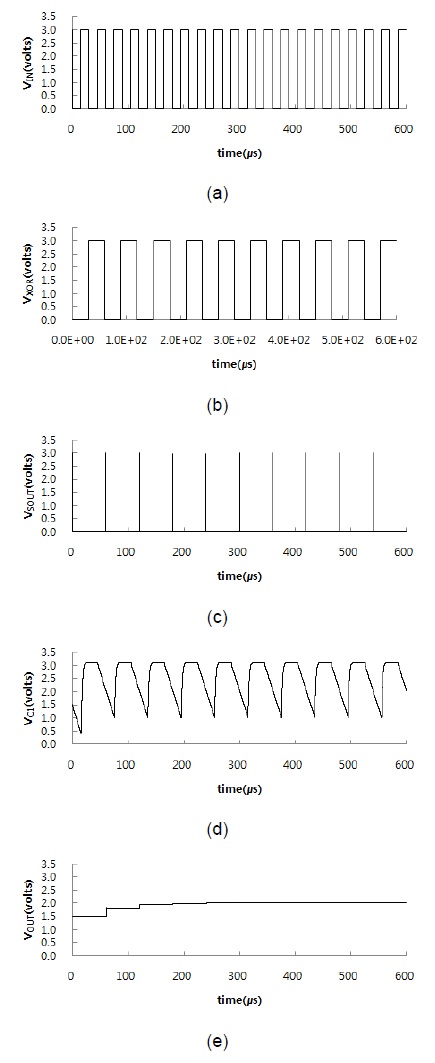

그림 5는 전류 컨베이어 회로를 이용한 주파수-전압변환 회로이며, 그림 6은 그림 5 회로의 출력파형이다[7]. 그림 6(a)는 입력 신호 VIN이며, 이 신호는 T 플립플롭의 클럭 단자에 인가된다. T 플립플롭의 출력 신호 VTOUT과 입력신호 VIN을 exclusive OR를 하면 출력 파형은 그림 6(b)와 같다. VXOR을 짧은 시간 지연시킨 다음, VXOR를 반전한 신호 /VXOR와 AND 하면 VXOR 신호가 ‘high’에서 ‘low’로 변화할 때, 그림 6(c)와 같은 듀티가 아주 짧은 VSOUT 신호가 생성된다. VSOUT 신호의 펄스 폭은 VXOR 신호를 지연시키는 지연 시간에 의해 결정되어 진다. 커패시터 C1의 전압은 VTOUT 신호가 ‘high’ 일 때 VDD로 충전하고, VTOUT 신호가 ‘low’ 일 때 전류 컨베이어 회로에 의해 전류 IX의 크기로 그림 6(d)와 같이 선형적으로 방전한다. VTOUT 신호가 ‘low’인 구간의 1/2 되는 시간에 VSOUT 신호는 ‘high’가 되고, 이 신호에 의해 C1의 전압은 C2로 전달되며, 파형은 그림 6(e)와 같다. 즉, 입력 신호의 주파수가 빨라지면, 방전하는 시간이 짧아져 C1에서 C2로 전달되는 전압은 증가하게 되고, 반대로 입력 신호의 주파수가 늦어지면, 방전하는 시간이 길어져 C2로 전달되는 전압 값은 작아진다.

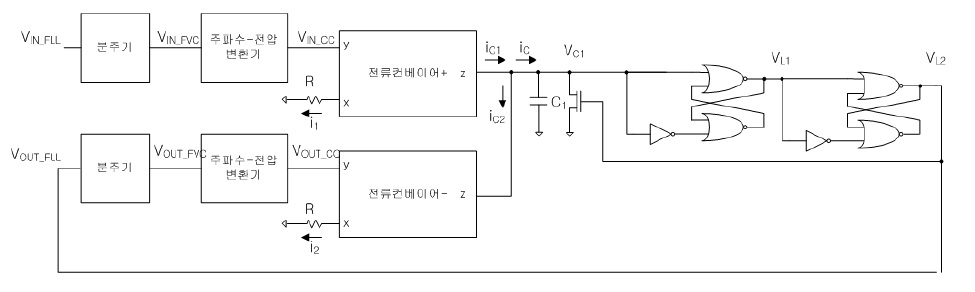

주파수 고정 루프 회로를 대칭적 구조로 설계하기 위하여 그림 3의 구조를 사용하였다[7]. 그리고 그림 3의 구조에서 주파수-전압 변환기의 출력 값의 차이를 구하는 감산기도 MOS 트랜지스터의 전기적인 특성 변화로 인한 영향을 상쇄할 수 있도록 대칭적 구조로 설계하였다. 그림 7은 그림 5의 주파수-전압 변환기를 이용하여 설계되어진 주파수 고정 루프 회로이다.

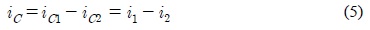

그림 7에서 주파수 변화에 따른 전압 차를 구하기 위해 전류컨베이어 회로를 이용하였다. 그림 7을 살펴보면, 분주기, 주파수-전압 변환기, 전압 차를 위한 전류컨베이어 회로는 대칭적 구조로 설계되어 레이아웃시 대칭적 구조로 레이아웃 되도록 설계하였다. VIN_FLL과 VOUT_FLL 신호는 T 플립플롭으로 구성된 분주기에 의해 분주된 다음, 주파수-전압 변환기에 입력되고, 주파수-전압 변환기에 의해 두 신호는 전압 신호로 변환된다. 그러므로 두 신호의 주파수 차이를 알기 위해서는 두 신호의 전압 차를 구하면 된다. 그림 7에서 두 신호의 전압 차를 구하기 위해 극성이 서로 다른 전류 컨베이어 회로를 이용하여 구성하였으며, 커패시터 C1에 충전되는 전류는 식 (5)와 같다.

여기서

VIN_CC의 전압이 증가하면 전류 i1이 증가하고 이로 인해 iC1이 증가한다. 이 경우 커패시터 C1의 전압이 임계전압에 도달하는 시간이 짧아져, 출력주파수는 증가할 것이다. 반대로 VIN_CC의 전압이 감소하면, 출력주파수는 감소할 것이다. 커패시터 C1에 충전되는 전압은 NOR 게이트로 구성된 래치의 출력 VL2가 'high'가 될 때까지 전류 iC에 의해 충전된다. C1의 충전전압이 임계 전압이 되면 래치의 출력 전압 VL2가 high가 되어 커패시터 C1은 방전한다. VC1이 low로 변화하면 다시 래치의 출력전압 VL2는 low가 되어 커패시터 C1은 충전하게 된다.

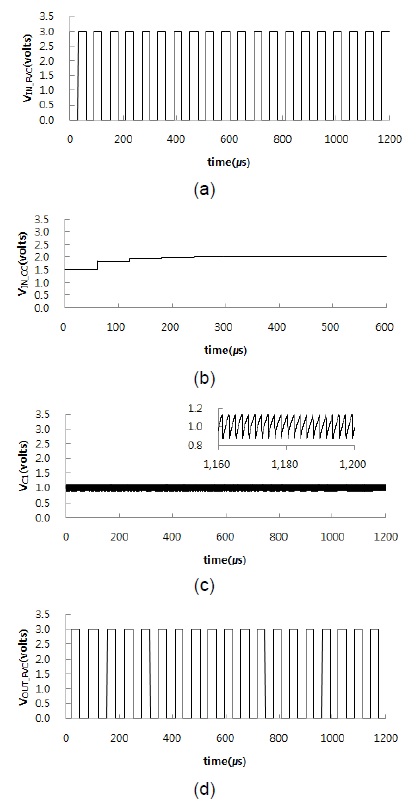

각 단자에서의 출력파형은 그림 8과 같다. 그림 8(a)는 VIN_FVC 신호로서 입력 신호 VIN_FLL을 32분주한 신호이다. 분주기의 출력 전압은 주파수-전압 변환기에 의해 그림 8(b)처럼 전압 신호로 변환된다. 커패시터 C1은 충방전을 하며, 파형은 그림 8(c)의 확대한 부분에서 보듯이 톱니파이다. 톱니파의 파형은 래치 회로를 거치면서 펄스파로 변화되고 32분주 회로를 거친 VOUT_FVC 파형은 그림 8(d)와 같다.

그림 7의 회로를 살펴보면, 입력신호 VIN_FLL과 출력신호 VOUT_FLL의 주파수를 전압으로 변환하고, 두 전압의 차이를 구하는 회로는 전류 컨베이어를 이용하여 대칭적 구조로 구성하였다.

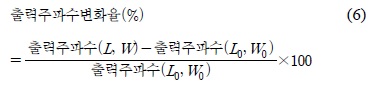

설계된 주파수 고정 루프 회로의 신뢰성 특성을 살펴보기 위해 사용된 MOS 트랜지스터의 채널 길이 및 폭을 변화시킨 다음, 식 (6)을 이용하여 출력주파수의 변화율을 계산하였다.

식 (6)에서 출력주파수(L,W)는 반도체 공정 진행에 따라 채널 길이 혹은 채널 폭이 변화하였을 때 주파수 고정 루프 회로의 출력주파수이고, 출력주파수(L0,W0)는 설계시 사용된 채널 길이 및 채널 폭으로서 공정 진행에 따른 채널 길이와 채널 폭이 변화되지 않았을 때의 출력주파수이다.

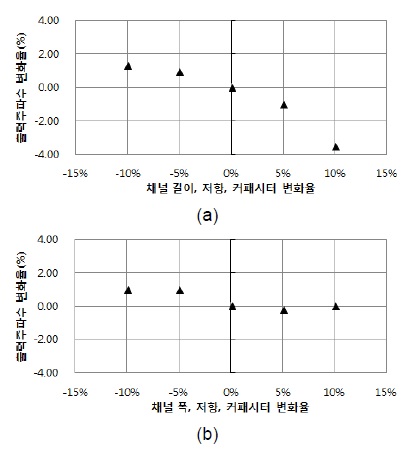

그림 9는 식 (6)에 의해 계산된 출력주파수의 변화율이다. 시뮬레이션을 위하여 채널 길이 및 폭의 변화에 따른 소자의 변화 조건은 다음과 같다.

여기서 저항과 커패시터는 게이트 폴리실리콘을 이용하여 구성하는 것으로 가정하였다. 그림 9(a)는 MOS 트랜지스터의 채널 길이, 저항, 그리고 커패시터의 값이 조건 (1)과 조건 (2)로 변화 할 때 식 (6)으로부터 계산된 출력주파수의 변화율이다. 그리고 그림 9(b)는 조건 (3)과 (4)와 같이 변화할 때 출력주파수의 변화율이다. 그림 9로부터 반도체 부품의 길이 및 폭의 변화가 ±5% 이내 일 때, 출력 주파수의 변화율은 ±1% 이내였다.

전류 컨베이어 회로를 이용한 주파수-전압 변환기와 전압 비교기를 구성하고, 래치를 이용한 발진기를 구성하여 주파수 고정 루프 회로를 설계하였다. 설계된 회로에서 주파수-전압 변환기 및 전압비교기를 대칭적 구조로 설계하고 배치하여 회로의 신뢰성 특성을 분석하였다. 채널 폭, 채널 길이, 저항과 커패시터 등의 크기가 공정 진행에 따라 ±5% 변화할 때 출력주파수의 변화율은 ±1% 이내로서 우수한 특성을 보여주었다.