이동통신 시스템의 OFDMA 방식은 신호에 대한 PAPR(Peak to Average Power Ratio) 값의 증가를 가져왔다. 이동통신 시스템 전력 소모의 대부분을 차지하는 전력 증폭기에 대한 효율 개선은 매우 중요한 핵심 기술이다. 전력 증폭기의 선형 특성 개선을 위해 디지털전치왜곡 기술을 사용하였으며, 전력 증폭기의 효율 개선을 위해 비대칭 도허티(Asymmetric Doherty) 방식을 사용하였다. 본 논문에서는 기존 비대칭 도허티 구조와 다른 새로운 구조의 비대칭 도허티 구조를 제안하였다. 제안하는 새로운 구조의 비대칭 도허티 방식에서는 전력 증폭기 구동단을 주경로와 첨두경로로 분리하였으며, 위상 변환기를 이용하여 도허티 증폭기의 전력 결합 특성을 개선하였다. 또한 구동단 첨두 증폭기 gate bais에 대한 포락선 추적 기술을 적용하여 효율을 개선하였다.

The PAPR of the input signal is increased due to OFDMA signal in a mobile communication system. High efficiency of a power amplifier, which accounts for power consumption, is a very important key technology. Digital Pre-Distortion techniques were used to improve the linearity of the power amplifier. The Asymmetric Doherty scheme was used to improve the efficiency of the power amplifier. In this paper, we propose a new structure of Asymmetric Doherty. Drive power amplifier part is separated as main path and peak path, and phase shifter is employed to improve power combine characteristics of the Doherty Amplifier. Also, envelope tracking technology for drive gate bais in drive peak amplifier is used to improve efficiency.

이동통신 시스템이 발전함에 따라 시스템 구성 모듈 중 전력 증폭기에 대한 성능 개선이 절실하게 되었다. 특히, 전력증폭기에 대한 선형성과 효율 개선이 전체 시스템의 효율을 좌우하게 되었다.

최근 전력 증폭기의 효율 개선 및 선형성 개선에 대해 많은 연구가 있었으며, 대표적인 기법은 디지털 전치왜곡 기법과 변조 신호의 포락선 추출을 통한 전압가변 기술인 포락선 추적 기술이 있다[1-3].

디지털전치왜곡 방식은 디지털 신호 처리를 통해 전력 증폭기 입력 신호 대비 출력 신호의 비선형 왜곡 정도를 확인하여 비선형 왜곡 신호와 진폭과 위상이 반대되는 신호를 입력 신호에 인가하여 전력 증폭기에 대한 선형 특성을 개선시키는 방식이다. 디지털전치왜곡 방식에는 LUT(Lookup Table)방식과 다항식 방식이 있으며, 본 논문에서는 다항식 방식을 적용하여 전력 증폭기의 선형성을 개선하였다. 디지털전치왜곡 기술은 초기 기지국 시스템에 주로 사용하였지만 현재는 이동통신 시스템에 광범위하게 사용하고 있다. 특히 광대역에 신호에 대해 대략 20~30dB의 선형성 개선 특성을 가지고 있다[4-5].

포락선 추적 기술은 변조 신호의 피크 값에 대한 포락선을 검출하여 실시간으로 신호 변화에 따른 바이어스 전압을 가변 시켜 증폭기 DC 전원이 RF 신호로 변환되면서 발생하는 열을 최소화시켜 전력 증폭기의 효율을 극대화 하는 방법이다. 게이트 바이어스 조절 방법은 도허티 증폭기 구조에서 효율 개선은 적지만 기존 동급 증폭기에 비해 선형 특성이 좋아 좀 더 높은 출력에 도달할 수 있다. 포락선 첨두치에 근거한 드레인 바이어스 조절 방법은 전력 증폭기가 항상 최대 출력에 도달 할 수 있게 DC 바이어스 상태를 유지해야 하며, 이로써 발생하는 효율 감소 문제를 해결할 수 있다. 또한 고정된 전압을 사용하는 기존 방식 대신 전력 증폭기에 전달되는 입력 신호의 크기에 따라 증폭기에 공급하는 전압의 크기를 가변함으로써 낮은 입력 신호에 대해 높은 효율을 유지한다[7].

본 논문에서는 1.8GHz 50W 고출력 전력 증폭기의 효율을 개선하기 위한 연구로 50% 이상의 효율과 -50dBc 이상의 ACLR(Adjacent Channel Leakage Ratio) 특성을 가지는 전력 증폭기를 연구한다. 50W 고효율 전력 증폭기 개발을 위해 본 논문에서는 크게 3가지 방식을 제안 하였다. 첫째 디지털전치왜곡 기술을 적용한 고출력 비대칭 도허티 전력 증폭기에 최적화된 최종 단 주 증폭기와 피크 증폭기의 구성을 찾고, 최적화 튜닝을 통해 전력 증폭기의 선형 특성 개선 및 효율 특성을 개선하였다. 둘째 비대칭 도허티 구조의 전력 증폭기 구동단 증폭기 구조를 단일경로 구조가 아닌 위상 변환기를 이용한 이중경로 구조로 변경하여 전력증폭기 효율을 개선하였으며, 위상 변환기를 이용하여 도허티 구조 전력증폭기 전력 결합에 대한 Load Transformation을 향상시켰다. 셋째 1.84GHz LTE 변조 신호의 세기에 따라 증폭기 바이어스에 공급되는 전압을 가변하여 전력 증폭기 효율을 개선하는 포락선 추적 기술을 적용하였다.

본 논문의 구성은 다음과 같다. 서론에 이어 II장에서는 비대칭 도허티 증폭기 설계 방안에 대해 설명하고, III장에서는 고효율 전력 증폭기 설계 및 제작을 통해 검증하였으며, 마지막으로 결론을 맺었다.

비대칭 도허티 증폭기는 일반 도허티 증폭기 보다 더 큰 백 오프 지점 확장을 위해 주 증폭기 출력이 더 낮은 지점에서 포화되어야 하고 피크 증폭기 동작점도 주 증폭기 포화점에 맞춰 출력이 이루어지도록 설계한다. 주증폭기가 낮은 전력에서 포화되기 위해서는 일반 도허티 증폭기 보다 더 높은 부하 임피던스가 되도록 적절한 공통 부하를 정해야 한다.[6]

비대칭 도허티 전력증폭기에서 신호에 대한 임피던스 매칭을 위해 전력 비율 계수(ρ), 공통부하(

여기서

디지털전치왜곡 전력 증폭기 back-off 값이 7.5dB를 가졌을 경우 식(1)를 통해 전력 비율(ρ) 값은 0.421이 되며, 공통 부하

또한, 비대칭 도허티 전력 증폭기는 주 증폭기가 포화되는 지점에 맞춰 피크 증폭기가 동작 되어야 선형성 및 효율 특성을 개선할 수 있기 때문에 낮은 지점에서 포화가 일어나는 주 증폭기와 균형을 맞추기 위해 C Class로 동작하는 피크 증폭기에 더 높은 신호 레벨이 입력되도록 입력 신호 분배를 결정해야 한다. 입력 전력 비율은 식(5)과 식(6)을 통해 전력 분배량을 결정할 수 있다.

7.5dB back-off를 가지는 디지털전치왜곡 전력증폭기에 대한 입력 전력 값을 구하면 주 증폭기는 -3.8dB, 피크 증폭기는 -2.3dB의 값을 구할 수 있다.

또한, 비대칭 도허티 전력 증폭기 설계를 위해서는 주 증폭기와 피크 증폭기에 대한 소자를 결정하여야 하며, 두 증폭기 소자의 합인 PEP(Peak Envelope Power) 는 식(7)과 같이 입력 신호 PAPR의 평균 출력 전력의 합보다 같거나 크게 설계하여야 선형성을 만족할 수 있게 된다. 전력 증폭기 출력이 47dBm이고 입력 신호의 PAPR이 7.5dB일 경우주 증폭기와 피크 증폭기에 대한 최대 피크 전력은 식(7)을 이용하여 구할 수 있다.

식 (7)을 통해 최대 피크 전력은 54.5dBm으로 281W 출력을 가져야 한다. 또한 주 증폭기 소자와 피크 증폭기 소자에 대한 용량은 식(8)과 식(9)을 이용하여 구할 수 있다.

식(8)과 식(9)을 적용하여 주 증폭기 소자의 용량을 계산하면 약 118W급이며, 피크 증폭기 소자의 용량은 162W급 소자를 사용하여야 한다.

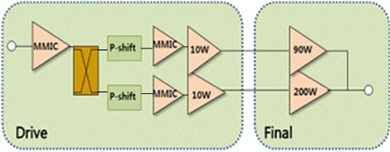

본 논문에서는 디지털전치왜곡 방식에 적합한 새로운 구조의 고출력 전력 증폭기를 제안한다. 그림 1은 제안한 비대칭 도허티 전력 증폭기 구조이다.

일반적인 비대칭 도허티 전력증폭기 구동단은 단일 경로로 최종 단 앞에 3dB coupler가 위치해 있지만 본 논문에서 제안한 비대칭 도허티 전력 증폭기는 구동단이 이중경로로 3dB coupler가 전력 증폭기 초단에 위치해 있으며, 구동단 경로를 주경로와 첨두경로로 나눴다.

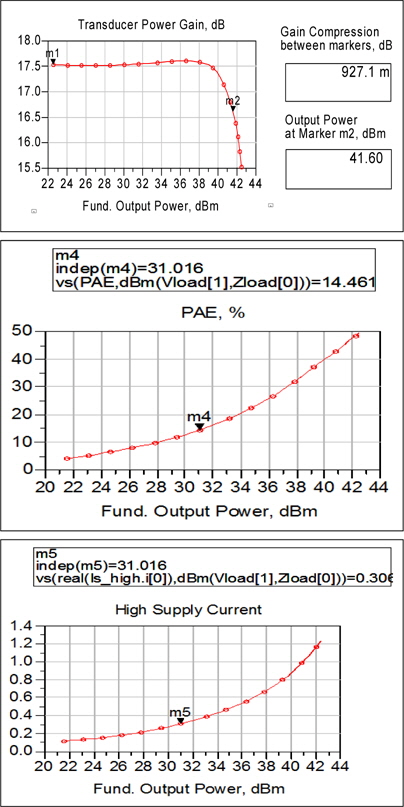

구동단이 단일경로일 경우 3dB coupler 손실 및 신호 IMD(Inter-modulation Distortion) 특성을 위해 구동단 증폭기의 back-off power를 더 많이 가져가야 하지만 본 논문에서 제안한 이중경로의 경우 구동단 증폭기 출력을 단일경로보다 3dB 낮게 가져 갈 수 있다. 또한, 위상 변환기는 비대칭 도허티 전력 증폭기 출력 신호 결합 시 위상에 대한 정밀 튜닝으로 전력 손실을 최소화 할 수 있으며, load transformation에 대한 어려움을 해결할 수 있다. 그림 2는 중심 주파수 1.84GHz 10W 구동단 최종 증폭기에 대한 전력 및 이득에 대한 시뮬레이션 데이터이다. 1.84GHz에서 전력은 41.6dBm으로 10W 이상의 전력를 가지고 있으며, 이득은 17.57dB, 효율 14.46%, 전류 300mA인 것을 확인할 수 있다.

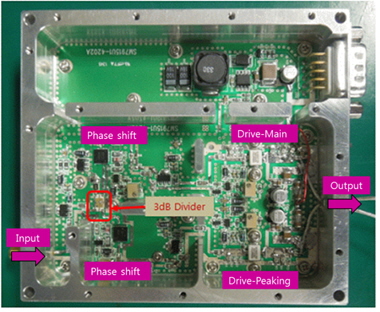

시뮬레이션 데이터를 기초로 제작된 구동단 증폭기는 그림 3과 같다. 초단 MMIC에서 증폭된 RF 신호는 3dB Coupler에서 주경로와 첨두경로로 나눠지며, 나눠진 신호는 위상 변환기 및 이득 블록을 지나 구동단 최종 증폭기에서 신호를 증폭 한 후 도허티 최종 증폭기로 입력된다.

위상 변환기를 이용한 이중경로 구동단은 약 20W급일 때 최종 단의 비선형성에 대한 보상 없이 출력을 만들 수 있다. 이때 요구되는 전력은 약 32dBm으로서 20W(43dBm) 대비 11dB의 back-off되는 지점에서 선형성을 유지할 수 있었으며 측정된 전류는 약 670mA, 효율은 8.5% 얻을 수 있다.

또한 구동단의 추가적인 효율 개선을 위해 주경로와 첨두경로에 대한 3dB coupler를 구동단 초단으로 변경하여 전력 손실을 줄였다. 주경로를 밀어주는 구동경로는 주경로가 포화될 수 있도록 전력 보다는 효율과 선형성 위주로 튜닝을 진행할 수 있으며, 첨두경로를 밀어주는 구동경로는 첨두경로 자체가 C급 동작이므로 선형화 보다는 첨두 전력 위주의 튜닝을 진행하였다.

한편, 구동단 각 경로에 대한 특성 차이와 최종 단 도허티 결합에 대한 보상을 위해 구동단 각 경로에 위상 변환기를 추가 하였다. 각 경로에 대한 위상을 조절하여 최종 단 전력 개선, ACLR 특성 개선 및 효율 보상 등의 효과를 얻을 수 있었다. 따라서 구동단을 기존 단일경로에서 이중경로로 변경함으로써 동일 출력 32dBm 을 기준으로 소모 전류 약 450mA까지 줄였으며, 효율은 12.7%까지 개선하였다. 줄어든 220mA 전류는 drive 자체에서 약 120mA 정도 개선하였으며, 위상을 조절하여 최종 단 도허티 임피던스 매칭을 통해 약 100mA 정도의 추가적인 전류를 개선하였다.

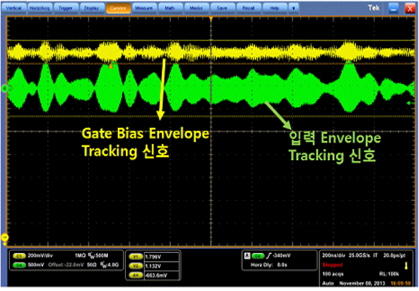

또한, 본 논문에서는 변조 신호의 크기에 따라 구동단의 첨두경로 게이트 전압을 조절하는 포락선 추적 기술을 적용하여 효율 개선 효과를 얻을 수 있었다. 게이트 가변 방식은 전력 증폭기의 선형 특성을 높여 보다 높은 출력에서 트랜지스터(Tr)를 사용할 수 있는 장점이 있다. 구동단 첨두경로의 게이트 바이어스를 변조 신호의 피크에 따라 트랜지스터를 능동적으로 조절하여 낮은 입력 시 구동단 피크 증폭기가 꺼지도록 하여 효율을 개선하였다.

최종 단 도허티 구조의 피크 증폭기도 일정 출력 이하일 때 동작하지 않기 때문에 첨두경로를 구동하는 구동단의 첨두경로 역시 동작 하지 않는다. 그림 4는 전력 증폭기에 공급되는 변조 신호의 포락선 추적 모습과 실제 구동단의 첨두경로쪽 게이트 바이어스의 포락선 추적 신호 모습이다. 구동단 피크 증폭기 게이트 바이어스 포락선 추적 기술을 적용하여 80 ~ 90mA의 전류 개선 효과를 얻었다.

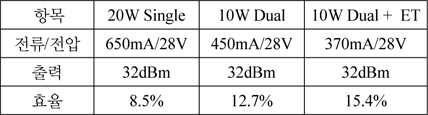

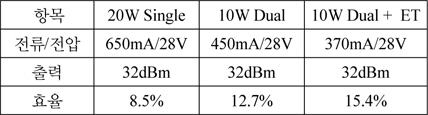

표 1은 전력증폭기 구동단에 대한 비교 시험 데이터이다. 고효율 증폭기 개발을 위해 포락선 추적 기술을 적용한 이중경로 구동단이 적합하며, 구동단 자체에 대한 효율을 15.4%까지 개선하였다.

구동단 특성 비교 데이터

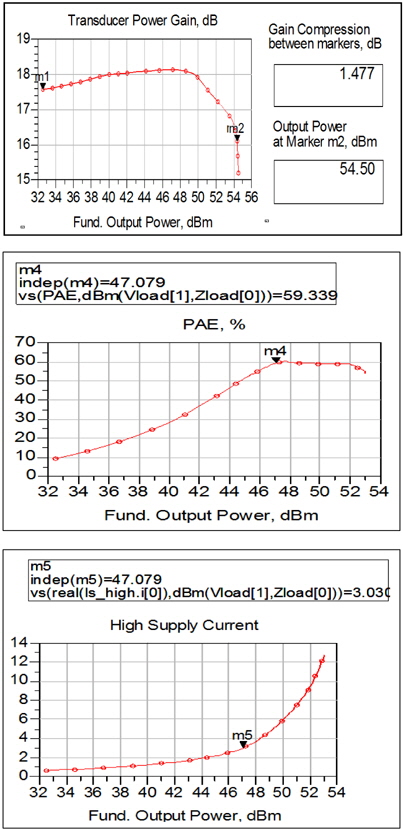

마지막으로 본 논문에서는 고효율, 고출력 전력증폭기 개발을 위해 디지털전치왜곡 방식에 적합한 비대칭 도허티 전력 증폭기의 최종 단에 대한 최적화 작업을 하였다. 최종 단에 대한 전력은 식 (7)을 통해 281W 이상 전력을 가져야 한다는 것을 알 수 있었으며, 식(8)과 식 (9)를 통해 주 중폭기와 피크 증폭기에 적합한 상용 트랜지스터를 결정하였다. 최종 트랜지스터 조합은 주 증폭기 90W, 피크 증폭기 200W 조합으로 증폭 소자를 구성하였으며, 전체 출력 전력은 290W로 이론상 요구하는 281W 이상의 전력용량을 만족하였다. 90W와200W 조합의 비대칭 도허티 증폭기에 대한 시뮬레이션 결과 이득은 17.36dB, 출력은 54.5dBm에서 281W, 효율은 59.3%, 전력 소모는 3A인 것을 확인 하였다.

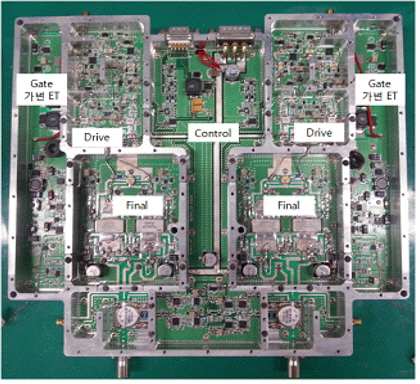

그림 6은 본 논문에서 제시한 새로운 구조의 비대칭 도허티 전력 증폭기에 대한 최종 제작 시료이다. 구동단 효율 개선을 위해 이중경로로 분리하였으며, 위상 변환기를 이용하여 최종 단 임피던스 매칭을 최적화 하였으며, 구동단 첨두경로에 대한 포락선 추적 기술을 적용하였으며, 선형성 개선을 위해 디지털전치왜곡 기술을 적용하였다.

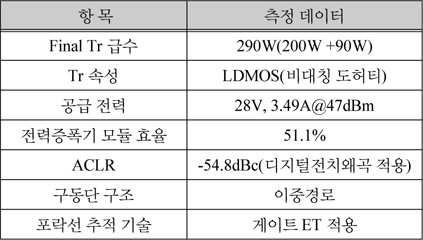

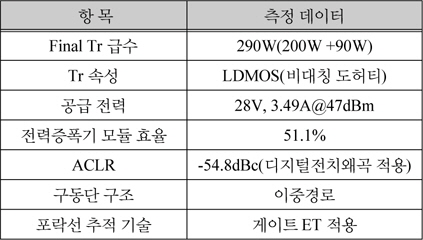

최종 개발된 디지털전치왜곡 증폭기에 적합한 비대칭 도허티 전력증폭기에 대한 특성은 표 2와 같다.

비대칭 도허티 최종 시료에 대한 특성

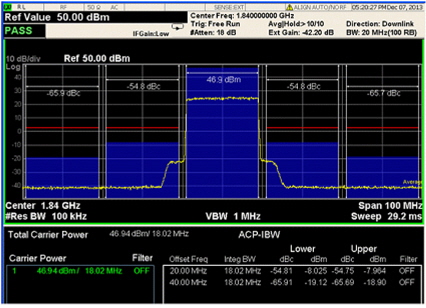

그림 7은 최종 개발 시료에 대한 ACLR 특성 데이터 를 나타내었다.

본 논문에서는 디지털전치왜곡 기술에 적합한 새로운 구조의 비대칭 도허티 전력 증폭기를 연구하였으며, 새로운 구조의 전력 증폭기를 이용하여 전력 증폭기 모듈 효율을 51%까지 증가시켰다. 새로운 구조의 전력 증폭기는 효율 개선을 위해 구동단을 주경로와 첨두경로로 나눠서 3dB coupler에 의한 전력 손실을 개선하였으며, 위상 변환기를 이용하여 최종 단 비대칭 도허티 증폭기 전력 결합에 대한 load transformation 특성을 정밀하게 조절하여 전체 전력 손실을 최소화하였다. 또한 구동단 피크 증폭기의 게이트 바이어스 전압을 변조 신호의 포락선 추적 신호에 맞춰 전압을 조절하여 구동단 전체 효율을 15.4% 개선할 수 있었다. 마지막으로 고효율 달성을 위해 디지털전치왜곡 기술에 적합한 도허티 증폭기 최종 단에 대한 최적화 작업을 진행하였다. 다양한 최종 단 주 증폭기와 피크 증폭기 조합에 대한 시제품 개발을 통해 90W와 200W 조합이 디지털전치왜곡 기술을 적용한 50W 고출력 전력증폭기 설계에 가장 적합하며, 효율 특성이 우수하다는 것을 확인할 수 있었다.