In this paper, the device design guideline to reduce the threshold voltage variation with fin width in junctionless MuGFET has been suggested. It has been observed that the threshold voltage variation was increased with increase of fin width in junctionless MuGFETs. To reduce the threshold voltage variation with fin width in junctionless MuGFETs, 3-dimensional device simulation with different gate dielectric materials, silicon film thickness, and an optimized fin number has been performed. The simulation results showed that the threshold voltage variation can be reduced by the gate dielectric materials with a high dielectric constant such as La2O3 and the silicon film with ultra-thin thickness even though the fin width is increased. Particularly, the reduction of the threshold voltage variation and the subthreshold slope by reducing the fin width and increasing the fin numbers is known the optimized device design guideline in junctionless MuGFETs.

최근에 나노미터 CMOS 소자의 단채널 현상을 줄이기 위해 무접합 소자가 제안되었다[1]. 무접합 트랜지스터는 기존의 벌크 MOSFET와 달리 채널과 소스/ 드레인의 불순물 종류와 농도가 같은 구조로 소스와 기판사이에 접합이 없는 구조이다. 무접합 소자는 소스/드레인과 기판 사이의 접합에서 불순물 농도 분포에 의한 단채널 현상과 기생 저항 성분을 줄일 수 있고 공정이 간단하므로 나노미터 레벨 CMOS 소자로서 유망한 것 으로 보고되고 있다. 무접합 트랜지스터는 SOI (Silicon–On-Insulator) 기술을 이용한 소자로 게이트 전압이 인가되지 않아도 실리콘 박막이 완전히 공핍상태가 되도록 하려면 제작 시 실리콘 박막 두께를 얇게 해야 한다. 트랜지스터가 오프 상태일 때 게이트와 실리콘의 일함수 차이로 박막을 완전히 공핍시키므로 드레인 전류가 흐르지 않게 된다. n-채널 무접합 트랜지스터는 게이트에 낮은 양의 전압을 인가하면 실리콘 박막이 부분적으로 공핍 상태가 되고 소스와 드레인의 전자가 실리콘 박막을 연결하면서 채널이 형성되는 즉 벌크 전도대역이 생성되어 전류가 흐르게 된다. 전류가 흐를 때의 게이트 전압을 문턱전압으로 정의하며 게이트에 문턱전압보다 더 큰 전압이 인가되면 Si 박막의 전체가 전자의 채널이 되는 평탄 전압 조건이 된다. 게이트에 평탄전압보다 더 큰 전압이 인가되면 마치 축적 모드의 트랜지스터와 같은 동작을 보이게 된다. 그 결과로 드레인 구동전류는 축적 모드 소자와 유사한 것으로 보고되고 있다[2].

무접합 MuGFET (Multiple Gate MOSFET)에서 Si박막의 두께, 산화층 두께, 채널의 불순물 농도, 핀 폭에 따른 문턱전압의 변화에 대한 많은 연구들이 진행되어 왔다 [3-5]. 무접합 트랜지스터는 벌크 전도대역에 의해 전류가 흐르게 되므로 표면에 채널이 형성되는 반전 모드 트랜지스터에 비해 표면 산란에 의한 이동도 감소는 적지만 채널의 불순물 농도가 매우 높으므로 실제 유효 이동도는 반전 모드보다 작게 된다[6]. 그리고 소스/드레인의 불순물 농도가 반전 모드 소자보다 작으므로 직렬저항이 상대적으로 크다는 단점이 있다[7]. 이를 해소하기 위해 소스/드레인에 한 번 더 불순물을 이온주입하여 소스/드레인의 불순물 농도를 높이기도 한다. 무접합 소자에는 채널 불순물 농도가 높으므로 나노미터 소자에서 불순물 농도의 변화에 따른 문턱전압 변화가 문제 될 것으로 제기 되었으나 심하지 않는 것으로 알려졌다[8]. 무접합 MuGFET를 집적회로에 응용한데 있어서 가장 큰 문제는 핀 폭에 따라 문턱전압의 변화 크다는 것이다. 핀 폭에 따라 문턱전압의 변화가 크면 집적회로 설계 시 어려움이 많으므로 가능한 문턱전압의 변화를 줄여야 한다. 최근에 32nm노드에서 15nm 노드로 소자의 크기가 축소되면 핀 폭에 따른 문턱전압의 변화가 디지털회로 레벨에서는 큰 문제가 되지 않는다는 연구도 발표되었다[9].

본 연구에서는 핀 폭에 따른 문턱전압의 변화를 줄이기 위한 무접합 트랜지스터의 소자 설계 가이드라인을 제시한다. 게이트 유전체, 실리콘박막의 두께, 핀 수를 최적화 하므로 핀 폭에 따른 문턱전압의 변화를 줄이는 소자 설계에 대한 연구를 수행하였다.

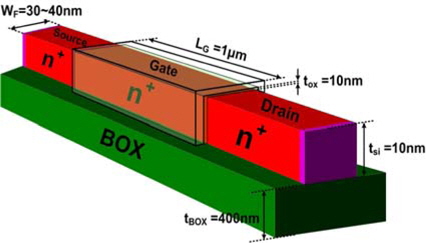

n-채널 무접합 MuGFET의 핀 폭에 따른 문턱전압변화를 측정하는 데 사용된 소자의 사양은 다음과 같다. 그림 1은 측정에 사용된 무접합 MuGFET의 도식도이다. 무접합 및 반전모드 MuGFET는 실리콘 박막의 두께가 340nm이며 저항이 10-20Ω-cm이고 매몰 산화층 두께가 400nm인 p-형 SOI 웨이퍼에 제작되었다. 자세한 공정과정은 참고문헌 [1] 에 자세히 서술되어 있다. 열산화 공정으로 실리콘 박막 두께를 10nm 되게 하였고 건식 산화 공정을 이용하여 게이트 산화층 두께가 약 10nm 되게 하였다. 무접합 소자의 채널 및 소스/드레인 농도가 약 ND=1x1019cm-3이고 반전모드 소자의 채널 농도 NA= 2x1018cm-3이다. 무접합 소자의 게이트는 P++로 도핑된 50nm 두께의 다결정 실리콘을 사용하였고, 반전모드 소자는 인을 이온주입하여 N++로 도핑하였다. 반전모드 소자는 비소를 각각 소스와 드레인 영역에 이온 주입하여 형성되었다. 최종적으로 제작된 소자는 게이트 확장 길이가 10nm인 Pi-gate 구조의 MuGFET이며 실리콘 박막 두께는 약 10nm이다. 측정에 사용된 모든 소자의 게이트 길이는 1㎛이고 핀 폭은 20nm, 30nm와 40nm이다. 그리고 핀 수는 1이다.

핀 폭에 따른 문턱전압의 변화를 줄이기 위한 무접합 MuGFET소자 설계는 3차원 소자 시뮬레이터인 Silvaco사의 ATLAS를 이용하였다. 소자 시뮬레이션에 사용된 소자 변수로는 게이트 산화층 두께가 3nm, 게이트 길이는 200nm 이다. 무접합 소자의 채널농도는 ND=1x1019cm-3 되게 균일하게 도핑 하였다. 소자 시뮬레이션에 사용된 물리적인 모델은 전계에 따라 변하는 이동도 모델, 속도포화 현상을 고려한 모델, SRH 재결합 및 생성 모델, 에너지 밴드갭 좁아짐 현상 모델 등을 포함하였다. 핀 폭, 게이트 유전체, 실리콘 박막의 두께, 핀 개수를 변수로 하여 소자 시뮬레이션을 수행하였다.

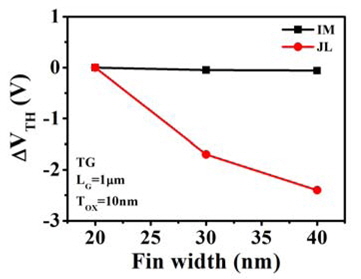

그림2는 n-채널 무접합 및 반전모드 MuGFET의 핀폭에 따라 측정한 문턱전압 변화를 나타낸 것이다. 반전모드 소자는 핀의 채널 폭이 증가하더라도 문턱전압의 변화가 거의 없으나 무접합 소자는 핀의 채널 폭이 증가하면 문턱전압이 크게 감소하는 것을 알 수 있다. 이런 결과는 기존에 발표된 타 연구 결과와 일치하는 것으로 무접합 소자를 집적회로에 응용하기 위해서는 문턱전압의 변화를 줄이는 연구가 필요하다 [5,10]. 무접합 MuGFET는 게이트 전압이 인가되지 않아도 게이트와 실리콘 박막의 일함수차이로 실리콘 박막이 완전히 공핍상태로 되어야 하는데 핀 폭이 증가할수록 측면 게이트에 의한 전계가 작게 되어 실리콘 박막을 완전히 공핍시키지 못하므로 실리콘 박막의 전자농도가 증가하게 된다.

그 결과로 핀 폭이 증가할수록 무접합 MuGFET의 문턱전압은 감소하는 것으로 사료된다. 참고문헌에 의하면 이중게이트 무접합 소자에서 핀 폭의 변화율(ΔW)에 따른 문턱전압의 변화율(ΔVTH)은 다음과 같은식으로 표시할 수 있다 [5].

여기서 COX는 게이트 커패시턴스이며 ND는 채널의 농도이다. 식 (1)로부터 핀 폭의 변화율과 채널의 불순물 농도가 증가하면 문턱전압의 변화율이 크게 됨을 알 수 있다. 그러나 식 (1)로부터 COX가 크면 문턱전압 변화율이 감소하는 것을 알 수 있다. 본 연구에서는 3차원 소자 시뮬레이션으로 COX를 크게 하기 위해서 고유전율을 갖는 게이트 유전체를 게이트 절연층으로 사용한 경우와 실리콘 박막의 두께에 따른 문턱전압의 변화율을 분석하므로 소자설계 가이드라인을 제공하였다.

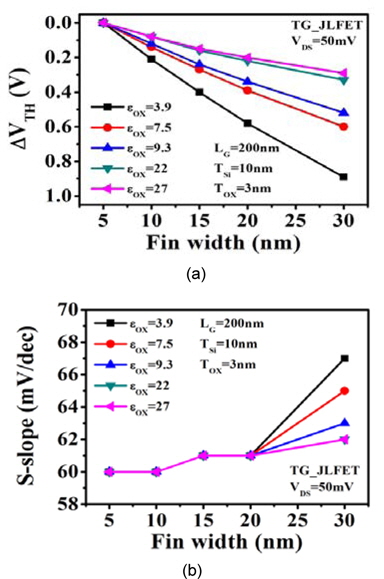

그림 3은 소자시뮬레이션에 의한 게이트 절연층의 유전상수가 다를 때 핀 폭에 따른 문턱전압 변화율과 문턱전압 아래 기울기(S)를 나타낸 것이다. 그림 3으로 부터 게이트 산화층으로 SiO2를 사용했을 때보다 고 유전율을 갖는 유전체를 게이트 절연층으로 사용할 때가 문턱전압의 변화가 작은 것을 알 수 있다.

이것은 식(1)에서와 같이 고 유전율을 갖는 유전체를 사용하면 COX가 증가하기 때문이다. 그림 3으로부터 유전율이 22 이상이면 핀 폭이 6배 증가해도 문턱전압의 감소가 0.3V 정도이므로 집적회로 응용에 문제가 없을 것으로 사료된다. 유전율이 27인 La2O3 유전체는 Si와 유전체 사이에 계면상태를 줄이기 위한 완충 게이트 산화층이 필요 없을 것으로 사료되므로 차세대 게이트 절연층으로 기대된다 [11]. 흥미로운 것은 핀 폭이 20nm이상으로 증가하면 유전율에 상관없이 모든 소자에서 S가 갑자기 증가하는 것이다. 이는 게이트 유전체를 SiO2를 사용하여 측정한 타 연구결과와 일치하는 것으로 무접합 MuGFET 소자설계 시 핀 폭의 변화에 따른 문턱전압의 변화도 중요하지만 S도 중요한 변수임을 보여준다[10]. 무접합 MuGFET의 이상적은 소자 특성을 위해서는 핀 폭을 너무 크게 하면 안 된다는 것이다.

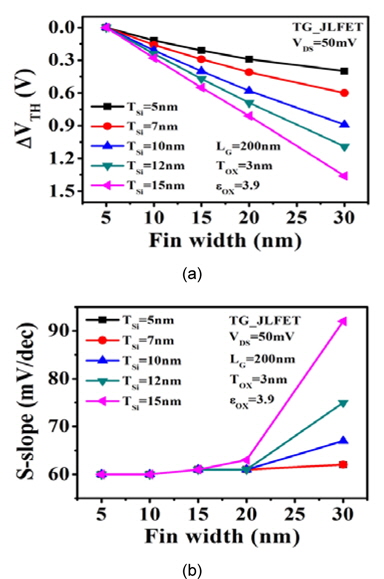

그림 4는 소자시뮬레이션에서 실리콘 박막 두께가 다를 때 핀 폭에 따른 문턱전압 변화율과 문턱전압 아래 기울기를 나타낸 것이다. 실리콘 박막의 두께가 증가할수록 핀 폭에 따른 문턱전압의 변화율이 큰 것을 알 수 있다. 이런 결과는 실리콘 박막의 두께가 증가할수록 게이트와 실리콘 박막의 일함수 차이로 실리콘 박막을 완전히 공핍시키기 어렵기 때문이다. 즉 실리콘박막의 두께가 증가하면 실리콘 박막의 전자 농도가 증가하기 때문에 문턱전압이 감소하게 된다. 그림3의 결과에서와 같이 실리콘 박막의 두께에 상관없이 핀 폭이 20nm이상이 되면 S가 급격히 증가하는 것을 알 수 있다. 실리콘 핀 폭이 20nm 이상이면 실리콘 박막이 상부게이트에 의해 완전히 공핍상태가 되지 않으므로 낮은 드레인 전압에서도 일부 벌크 전도대역이 형성되어 S가 급격히 증가하는 것으로 사료된다.

3.3. 핀 폭에 따른 문턱전압 변화율을 줄이기 위한 소자설계 가이드라인

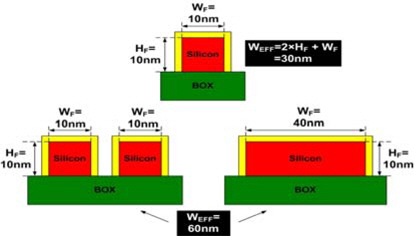

MuGFET를 사용한 집적회로 설계 시 구동전류를 크게 하기 위해서는 핀 폭을 크게 하거나 핀 수를 많게 하면 된다. 그림 3과 4의 결과로부터 핀 폭이 증가하면 문턱전압의 변화율과 S 특성이 좋지 않으므로 MuGFET소자 설계 시 핀 폭을 작게 하면서 핀 수를 증가 시키는 것이 바람직하다. 본 연구에서는 MuG- FET의 유효 채널 폭(WEFF)을 일정하게 하고 핀 수를 다르게 하므로 문턱전압과 S의 특성을 비교 분석하였다. 그림 5는 유효채널 폭이 60nm로 동일하면서 핀 수를 1로 하였을 때 와 2로 하였을 때의 레이아웃 도식도이다. 소자의 특성을 비교 분석하기 위해 유효채널 폭이 30nm인 소자를 기준으로 하였다.

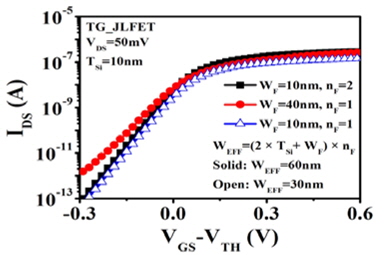

그림 6은 기준 소자, 핀 수가 1인 소자 및 핀 수가 2인소자의 문턱전압 아래 특성을 나타낸 것이다. 그림으로 부터 핀 수를 2로 하였을 때는 기준 소자와 같은 문턱전압 아래 특성을 보이나 핀 수를 1로 하였을 때는 누설전류 및 S 값이 증가하는 것을 알 수 있다. 그러나 드레인구동전류는 핀 수와 상관없이 거의 동일한 것을 알 수 있다. 그림에서와 같이 핀 수가 1일 때 누설전류가 증가하고 S가 큰 것은 무접합 소자에서 핀 폭이 증가할수록 실리콘 박막이 완전히 공핍되지 않고 잔류 전자의 농도가 높기 때문이다. 잔류 전자를 게이트 전압으로 완전히 제어할 수 있으면 누설전류나 S값이 감소하게 되지만 핀 폭이 증가하면 측면 게이트의 제어 능력이 떨어지므로 잔류 전자의 농도가 증가하게 된다.

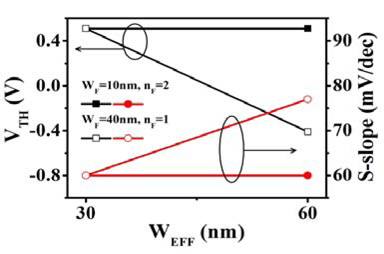

그림 7은 유효 채널 폭이 60nm로 동일한 조건에서 핀 수를 1과 2로 하였을 때의 문턱전압 변화율과 문턱전압 아래 특성을 나타낸 것이다. 핀 수를 1로 하였을 때는 문턱전압의 변화율이 크지만 핀 수를 2로 하였을 때는 문턱전압의 크기가 기준 소자와 동일하게 된다. 그리고 핀 수가 1인 소자는 S 가 크지만 핀 수가 2인 소자는 기준 소자와 S 값이 같게 된다.

그림 6과 7의 결과로부터 무접합 MuGFET 소자를 설계 시 핀 폭의 증가에 따른 문턱전압 변화율을 줄이고 문턱전압 아래 기울기를 작게 하기 위해서는 핀 하나의 폭은 작게 하면서 핀 수를 증가 시키는 것이 바람직한 설계 방법임을 알 수 있었다. 무접합 소자는 소자의 공정에서 발생하는 물리적 크기의 편차에 따른 문턱전압 변화율이 크므로 집적회로 응용에 어려울 것으로 주장하는 연구도 있으나 고 유전율을 갖는 게이트 유전체를 사용하고 핀 수를 많게 하면 핀 폭에 따른 문턱전압 변화를 줄일 수 있으므로 15nm노드 공정에서는 문제가 없을 것으로 사료된다.

무접합 MuGFET 소자의 핀 폭 증가에 따른 문턱전압의 변화율을 줄이기 위한 소자 설계 가이드라인을 제시하였다. 고 유전율을 갖는 La2O3 유전체를 게이트 절연층으로 사용하거나 실리콘 박막을 최대한 얇게 하므로 핀 폭이 증가해도 문턱전압 및 문턱전압 아래 기울기 변화율을 줄일 수 있음을 알 수 있었다. 그리고 무접합 MuGFET 소자 설계에서 문턱전압 변화율 못지않게 문턱전압 아래 기울기를 고려하여 핀 폭을 결정해야 함을 알 수 있었다. 특히 유효 채널 폭을 같을 때 넓은 핀폭 대신 핀 수를 많게 하므로 문턱전압 변화율과 문턱전압 아래 기울기를 작게 하는 것이 최적의 소자 설계가이드라인임을 알 수 있었다.