This paper suggest an effective idea to implement an low area multi-mode one dimension transform block of HEVC(High Efficiency Video Coding). The time consuming multiplier path is designed to operate on low frequency. Normal multipliers dealing with variable operands are replaced with smaller constant multipliers which do the product with constant coefficient and variable only using shifters and adders. This scheme increases total multiplier counts but entire areas are reduced owing to smaller area of constant multiplier. Idle cycles caused by doubled multipliers enable to use multi-cycle paths on the cycle eating multiplier data path. Operating frequency is lowered by multi-cycle path but total throughput is maintained. This structure is implemented with TSMC 0.18 CMOS process library, and operated on 186MHz frequency to process a 4k(3840x2160) image. Max operating frequency is 300MHz.

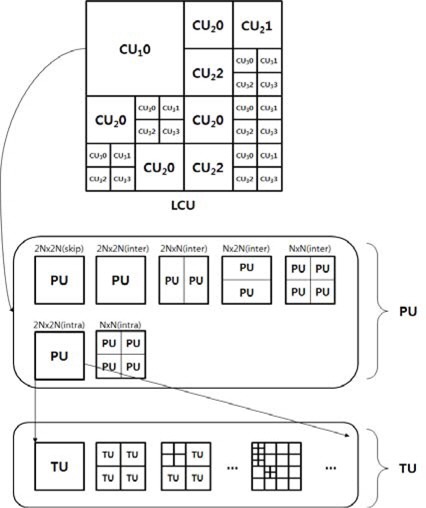

HEVC는 고화질, 고해상도의 영상을 위한 비디오 압축 코덱으로 압축 효율을 높이기 위해 CU(Coding Unit), PU(Prediction Unit), TU(Transform Unit)와 같은 다양한 블록을 지원하며 각각 블록에서도 다양한 사이즈를 지원하고 있다[1]. H.264/AVC에 비해 2∼4배 증가된 여러 종류의 블록 크기를 사용하는 특징과 내부 연산의 복잡도 증가로 인하여 연산량이 급증하기 때문에 하드웨어로 구현할 시 전체 면적이 커지는 단점을 가진다.

본 논문에서는 HEVC 부호화기 블록 중 특히 처리하는 기본 블록의 크기에 영향을 받는 변환 블록의 최적화된 설계 방법을 제시한다. 또한 다양한 처리 블록의 크기를 모두 지원하는 변환 블록을 제안한 방법으로 구현하여 저면적을 소요하고 고성능의 처리율을 보이는 다양한 블록 크기를 지원하는 변환 블록의 효율성을 입증하였다.

현재 쓰이고 있는 영상 압축 코덱인 H.264/AVC의 변환블록은 공간적 영역의 데이터를 주파수 영역으로 바꾼 후 중요도가 떨어지는 데이터를 제거하여 압축률을 높이는 방법을 공통적으로 사용하고 있다. DCT 연산은 기본적으로 행렬연산으로 구성되어 있으며 효과적인 하드웨어 구현을 위한 여러 가지 방법들이 제시되고 있다. 제시된 여러 가지 방법들 중 행렬을 재구성하여 축소된 복수의 행렬을 이용해 연산량을 줄인 방법인 Chen 알고리즘을 많이 사용한다. 수식 1은 Cosine의 주기 특성을 이용하여 중복 계산을 줄인 Chen 알고리즘 중 DCT 부분이다.

변환 연산은 처리하는 블록의 크기에 따라 비례하여 전체 크기가 커지는 경향을 갖는다. 특히 현재 그 표준이 정해지는 단계에 있는 HEVC의 경우, 압축률을 높이기 위해 영상의 특성에 따라 처리하고자 하는 블록의 크기가 최소 4x4에서 최대 32x32까지 가변하게 되는데 이러한 블록 크기에 비례하여 사용되는 연산기의 수가 증가하기 때문에 효율적인 설계 방법이 더 중시된다. 그림 1은 HEVC에서 사용하는 TU의 구조이다.

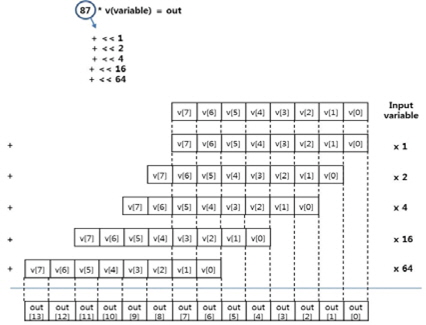

곱셈기는 그 크기가 다른 연산기들에 비해 크기 때문에 곱셈기의 크기를 줄이려는 많은 노력이 이루어져 왔다. 근래에는 변환 연산에 쓰이는 곱셈 연산이 일반적인 변수와 변수와의 곱셈이 아니라 고정된 상수와 곱셈과의 연산을 이용하여 시프트 연산과 덧셈기만을 이용하여 곱셈을 수행하는 방법을 많이 사용하고 있다[2].

앞 장에서 살펴본 바와 같이, 변환 블록은 다양한 블록 크기를 지원하여 크기가 커질수록 연산기의 수가 늘어나는 특성으로 인하여 하드웨어로 구현할 시 전체 크기가 커지는 단점을 가진다[3].

이러한 단점을 해결하고자 근래에는 고정된 상수와 곱셈과의 연산을 이용한 방법을 많이 사용하고 있다. 제안하는 변환 연산은 이러한 방법을 이용하는 동시에 누산기와 멀티 사이클 구조의 곱셈기를 사용하였다.

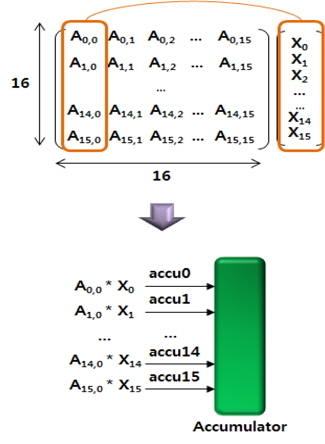

변환 블록에서 사용되는 행렬 연산은 블록 크기가 32x32일 때 그림 2에서 볼 수 있듯이 16x16의 상수로 이루어진 행렬과 16x1의 입력 데이터의 곱이다. 한 클록 당 한 개의 데이터를 처리하기 위해 최소 한 개의 행에 해당하는 16개의 일반적인 변수와 변수의 연산을 처리하는 일반적인 곱셈기가 필요하게 된다. 본 논문에서는 변환 행렬의 곱이 정해져 있는 상수와 변수인 입력 데이터와의 곱임을 이용하여 면적이 작은 시프트 연산과 덧셈기만으로 구성되는 입력되는 변수와 상수와의 곱셈기를 구성하여 사용하였다.

그림 3은 시프트와 덧셈기만으로 구성되는 변수와 상수와의 곱셈기 구조이다. 상수와 변수 곱셈기는 정해진 상수에 대하여 개별적으로 곱셈기를 사용하기 때문에 상수의 수만큼의 곱셈기가 필요하다.

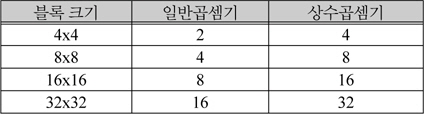

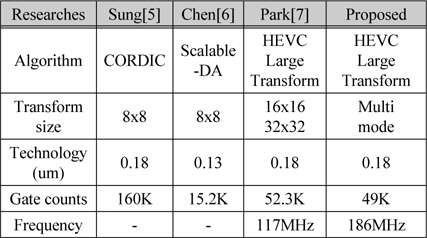

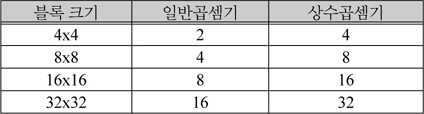

표 1은 재구성된 HEVC의 변환 행렬을 상수 곱셈기로 처리할 때 필요한 상수 곱셈기의 개수를 블록의 크기에 따라 정리한 표이다. 일반적으로 곱셈기를 사용할 때보다 두 배의 개수인 곱셈기가 필요하지만 일반적으로 상수 곱셈기의 크기가 일반 곱셈기보다 크기가 훨씬 작기 때문에 전체 크기는 줄어들 것으로 기대할 수 있다.

[표 1.] 블록 크기에 따른 일반 곱셈기와 상수 곱셈기의 사용 개수 비교

블록 크기에 따른 일반 곱셈기와 상수 곱셈기의 사용 개수 비교

제안하는 변환 블록은 누산기를 사용하여 행렬 연산 값을 구한다. 최소의 클록 주기 안에 행렬 연산을 완료하기 위해서는 상수곱셈기의 활용을 최대로 하여야한다. 변환 연산의 계수 특성상 일반적인 행과 열의 곱을 수행하면 매 클록동안 모든 상수 곱셈기를 활용한 연산을 할 수 없다. 따라서 본 논문에서는 행과 열의 연산 대신 앞서 보았던 그림 3에서 볼 수 있듯이 열과 열의 연산을 수행하도록 하였다. 이렇게 하면 변환 행렬의 계수 특성 상 매 클록마다 모든 상수 연산기를 활용할 수 있기 때문에 전체 행렬 연산에 필요한 클록 수를 최소화 할 수 있을 뿐만 아니라 상수 곱셈기의 수가 일반적인 곱셈기의 수보다 두 배가 되기 때문에 전체 연산처리량도 두 배가 되는 장점을 가진다.

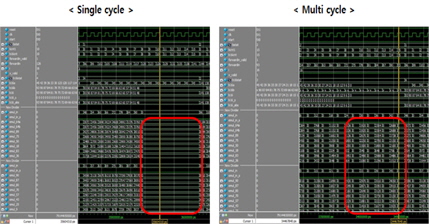

증가한 상수 곱셈기의 수로 인해 단위 시간당 연산 처리량은 입력되는 데이터의 양보다 두 배가 된다. 이것을 이용하여 가장 시간이 많이 걸리는 데이터 패스인 곱셈기 부분을 멀티 사이클 구조로 구현하여 전체적인 동작 주파수를 높였다. 그림 4는 단일 사이클 동작 모드에서의 변환 블록의 변환 연산 결과 값 시뮬레이션 파형과 멀티 사이클 패스를 적용한 변환 블록의 변환 연산 결과 값 시뮬레이션 파형을 비교한 것이다. 단일 사이클 패스의 경우 실시간 처리에서의 단위 시간당 데이터의 양은 일정하기 때문에 주어진 데이터를 처리하고도 여분의 시간이 남는다. 하지만 연산 시간이 많이 걸리는 곱셈기 부분에 멀티 사이클 패스를 적용시켜 동일한 양의 데이터를 처리할 경우 단일 사이클 패스에서의 처리하는 주파수와 비교했을 때 보다 연산량 처리율이 향상되고, 낮은 주파수에서 동작 시킬 수 있다.

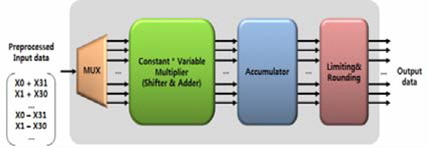

제안하는 변환 블록의 구조는 그림 5와 같다. 전처리된 데이터는 매 사이클마다 MUX를 통해 적절한 타이밍에 곱셈기로 입력된다. 곱셈기에서 연산된 값을 누산기에서 받아 앞서 기술한 제안하는 변환 연산을 이용하여 행렬 연산을 한다. 그 후 라운딩을 거쳐 출력 데이터를 내보낸다.

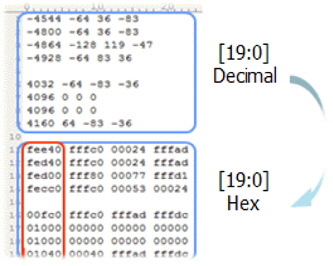

구현한 변환 블록은 HM 참조 소프트웨어의 변환 블록 연산 중 결과물을 추출하여 구현한 변환 블록 연산 중 결과물과 비교하여 검증하였다[4]. 그림 6은 구현한 변환 블록의 검증을 위하여 추출한 HM-10.0rc1 참조 소프트웨어 변환 블록의 변환 연산 결과 데이터 값이다. 구현한 변환 블록의 연산 결과 값과 비교를 쉽게 하고자 10진수와 16진수의 결과 값을 추출하여 비교하였다.

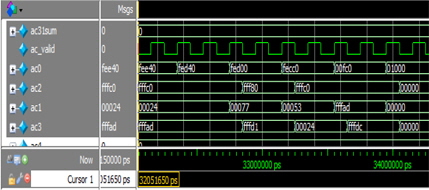

그림 7은 구현한 HEVC 변환 블록에서의 변환 행렬 연산 결과에 대한 시뮬레이션이다. 그림 6의 16진수 결과 값과 그림 7의 16진수 결과 값을 비교했을 시 동일한 값이 나옴을 확인할 수 있다.

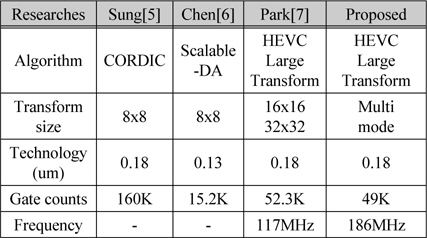

제안하는 변환 블록은 Verilog HDL로 설계한 RTL 코드를 TSMC 0.18um CMOS 고정의 라이브러리와 함께 IDEC에서 지원하는 Synopsys 사의 Design Compiler를 통해 합성했다. 총 게이트 수는 49k이고, 4k(3840x2160)@30fps 영상을 동작 주파수 186MHz로 처리하였다. 표 2는 기존에 제안되었던 1D 변환 블록들의 구조와 제안하는 1D 변환 블록을 비교한 것이다.

표에서 알 수 있듯이 총 게이트 수는 최근 제안된 구조와 비교하여 감소하였다. 제안한 구조는 4k@30fps 영상의 YCbCr값을 변환 블록에서 처리되는 1D 변환 블록의 사이클 수는 176이다. 따라서 2D 변환 블록을 구현하여 처리했을 시 제안된 구조에 비해 적은 사이클을 사용한다. 4k 영상을 처리하기 위한 최소 동작 주파수는 186MHz이고 최대 동작 주파수는 300MHz이다.

[표 2.] 기존에 제안된 1D 변환 블록 구조들과 제안한 1D 변환 블록 구조와의 비교

기존에 제안된 1D 변환 블록 구조들과 제안한 1D 변환 블록 구조와의 비교

최근 제안된 구조[5]는 4k@30fps 영상 중 Y값만을 변환 블록에서 2D 변환 블록에서 처리되는 사이클 수가 481이고 최소 동작 주파수는 117MHz라는 점과 비교를 하였을 시 제안한 구조가 향상됨을 알 수 있다.

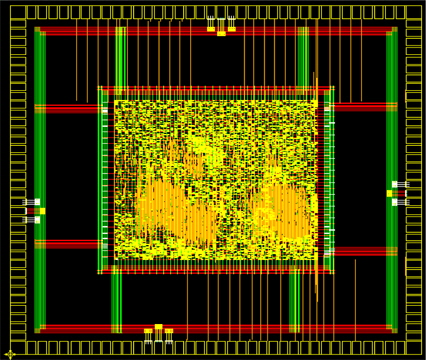

그림 8은 TSMC 0.18um CMOS 공정 라이브러리로 구현한 제안하는 1D 변환 블록의 레이아웃이다.

본 논문에서는 블록 크기를 최대 32x32 크기까지 지원하는 차세대 영상압축코덱인 HEVC 부호화기용 변환 블록을 효율적으로 구현하는 방법을 제시하였다. 기존에 제시된 변환 행렬의 계수 특성을 이용하여 전체 면적을 줄일 수 있는 상수 곱셈기를 사용하였고 기존의 변환 블록 하드웨어 구조와는 달리 계산 시간이 오래 걸리는 곱셈기 부분은 멀티 사이클 패스로 적용하여 보다 낮은 주파수에서 고화소 영상을 처리할 수 있고 용이하게 다중 블록 처리가 가능한 행렬 연산기를 구현하였다. 4k@30fps 영상을 처리하는 것을 기준으로 최근 제안된 구조와 비교했을 때 제안된 구조는 2D 변환 블록을 481 사이클 수를 사용한 반면 본 논문에서 제안한 구조는 1D만 구현하여 176 사이클이 걸렸다는 점이 최근 제안된 구조보다 적은 사이클로 동작하는 효율적인 구조임을 입증하였다.