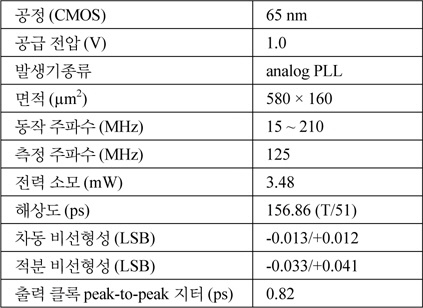

본 논문에서는 125 MHz 목표 주파수의 51-위상 출력 클록을 가지는 전하 펌프 위상 고정 루프(PLL)를 제안한다. 제안된 위상 고정 루프는 51-위상 클록을 출력하면서 최대 동작 주파수를 확보하기 위해 세 개의 전압 제어 발진기(VCO)를 사용한다. 17 단의 지연 소자는 각각의 전압 제어 발진기를 구성하며, 51-위상 클록 사이의 위상 오차를 줄이는 저항 평준화 구조는 세 개의 전압 제어 발진기를 결합시킨다. 제안된 위상 고정 루프는 공급전압 1.0 V의 65 nm 1-poly 9-metal CMOS 공정을 사용한다. 동작 주파수 125 MHz에서 시뮬레이션된 출력 클록의 peak-to-peak 지터는 0.82 ps이다. 51-위상 출력 클록의 차동 비선형성(DNL)과 적분 비선형성(INL)은 각각 −0.013/+0.012 LSB와 −0.033/+0.041 LSB이다. 동작 주파수 범위는 15 ~ 210 MHz이다. 구현된 위상 고정 루프의 면적과 전력 소모는 각각 580 × 160μm2과 3.48 mW이다.

This paper proposes a charge-pump phase-locked loop (PLL) with 51-phase output clock of a 125 MHz target frequency. The proposed PLL uses three voltage controlled oscillators (VCOs) to generate 51-phase clock and increase of maximum operating frequency. The 17 delay-cells consists of each VCO, and a resistor averaging scheme which reduces the phase mismatch among 51-phase clock combines three VCOs. The proposed PLL uses a 65 nm 1-poly 9-metal CMOS process with 1.0 V supply. The simulated peak-to-peak 지터 of output clock is 0.82 ps at an operating frequency of 125 MHz. The differential non-linearity (DNL) and integral non-linearity (INL) of the 51-phase output clock are −0.013/+0.012 LSB and −0.033/+0.041 LSB, respectively. The operating frequency range is 15 to 210 MHz. The area and power consumption of the implemented PLL are 580 × 160μm2 and 3.48 mW, respectively.

최근 인터페이스 응용 분야에서 보다 큰 대역폭이 요구됨에 따라 그래픽 메모리, 메인 메모리, 그리고 모바일 메모리까지 입/출력 동작속도는 지속적으로 증가하고 있다. 따라서 메모리에서도 직렬 인터페이스에서 사용되는 입/출력 설계 기술이 도입되기 시작하였고, 이를 검증하기 위해 고가의 장비를 포함한 테스트 솔루션이 개발되었다. 특히 칩-to-칩 인터페이스의 특성을 검증하기 위해 실시간 오실로스코프, 비트 오류 검사기와 같은 측정 장비가 사용된다. 그러나 인터페이스 속도가 10 Gb/s 까지 요구되면서 보다 더 성능이 우수한 고가의 측정 장비가 필요하게 되었다. 하지만 고가의 장비로 칩 입/출력 단자에 대해 신호의 특성을 분석하더라도 실제 칩 내부 상황을 정확하게 파악하기 어렵다. 이것은 칩의 핀에서 분석된 특성이 칩 패키지와 칩 내부의 전원 무결성 및 신호 무결성에 따라 칩 내부 입/출력회로에서 보이는 특성과 동일하기 않기 때문이다. 칩내부 고속 신호를 측정 장비로 직접 측정하기 위해서 별도의 핀을 배치하면 연결 배선의 R/L/C 성분과 주변신호에 의한 심볼간 간섭(ISI), 크로스토크등과 같은 노이즈에 의해 손실이 발생된다.

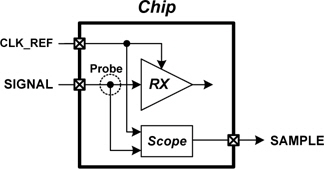

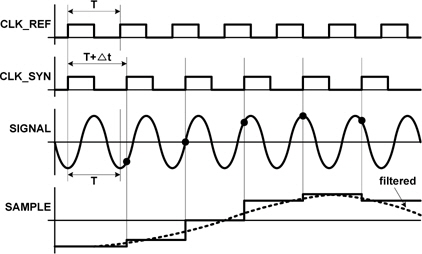

위에 언급된 문제점을 해결하기 위해서 칩 내부에서 신호를 측정할 수 있는 그림 1과 같은 온-칩 오실로스코프를 사용할 수 있다[1]. 이 회로는 SIGNAL을 서브 샘플링하여 샘플된 데이터를 디지털 신호로 출력한다. 출력된 디지털 신호를 외부에서 측정 후 신호를 복원하여 신호의 특성을 파악할 수 있다. 출력 신호는 SIGNAL을 서브 샘플링한 디지털 신호이기 때문에 R/L/C 성분 및 ISI와 같은 노이즈에 강하여 측정이 용이하며 낮은 주파수를 가지기 때문에 고속 측정 장비가 요구되지 않는다. 그러므로 온-칩 오실로 스코프는 고속 신호를 측정하는데 비용과 노력을 절약할 수 있다.

그림 2는 온-칩 오실로스코프의 타이밍도이다. SIGNAL은 CLK_SYN 클록을 이용하여 서브 샘플링하고 내부 아날로그 디지털 변환기(ADC)가 이것을 디지털 신호로 변환하여 출력한다. CLK_REF의 주기 T보다 Δt 증가된 CLK_SYN은 주파수 합성기를 이용하여 구현한다. 주파수 합성기는 사용될 시스템에 따라서 다중-위상 클록 발생기[1][2] 또는 분수 분주형[3]으로 구성된다.

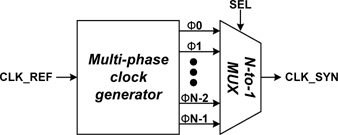

그림 3은 CLK_REF를 이용하여 새로운 주파수를 가진 CLK_SYN을 출력하기 위한 다중-위상 클록 발생기 기반의 주파수 합성기 블록도이다. 주파수 합성기의 주파수 가변 해상도는 다중-위상 클록 발생기의 N에 의해서 결정되고 Δt 는 주기적 선택 신호인 SEL에 의해서 결정된다. 이와 같은 주파수 합성기는 통신 시스템에서 라디오 주파수(RF)를 중간 주파수(IF)로 변환하거나 IF를 RF로 변환할 때 국부발진기로도 사용되며, 여러 개의 채널을 갖는 송수신 시스템에서 원하는 채널을 선택하는 기능을 한다. 이때 빠른 고정 시간이 요구되기 때문에 분수 분주형 보다 빠른 고정 시간을 제공하는 다중-위상 클록 발생기 기반의 주파수 합성기를 이용할 수 있다.

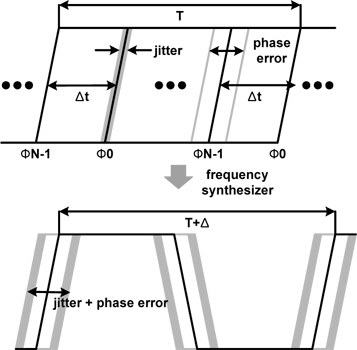

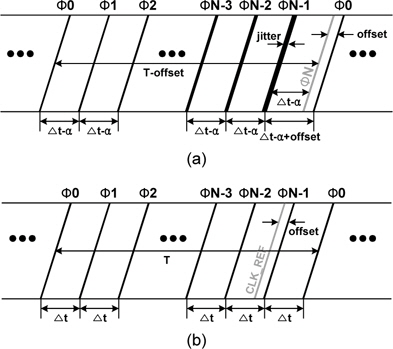

그림 4는 다중-위상 클록 발생기에 위상 오차와 지터가 발생했을 때 주파수 합성기의 출력 클록 지터 영향을 나타낸다. 주파수 합성기는 N개의 출력 위상 클록을 한 번씩 모두 선택하기 때문에 출력 클록 지터는 최대 위상 오차와 지터를 합한 수치로 정의된다. 즉, 다중-위상 클록 발생기의 위상 오차와 지터는 주파수 합성기의 성능을 좌우하게 된다.

Ⅱ. 다중-위상 출력 클록을 가지는 DLL과 PLL 성능 분석

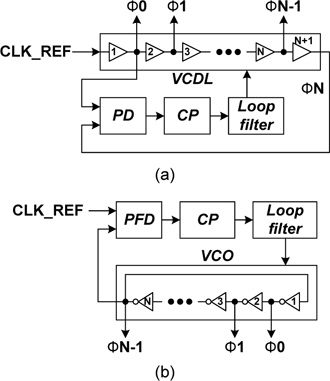

그림 5(a)와 (b)는 기존의 다중-위상 출력 클록을 가지는 지연 고정 루프(DLL)와 위상 고정 루프(PLL) 블록도이다. 그림 5(a)의 DLL은 위상 검출기(PD), 전하 펌프(CP), 루프 필터(LP), 전압 제어 지연 라인(VCDL)으로 구성된다. 특히 VCDL은 N-위상 클록을 위해 N+1개의 지연 소자로 구성된다. 그림 5(b)의 PLL은 DLL에서 PD와 VCDL대신 위상 주파수 검출기(PFD)와 전압 제어 발진기(VCO)를 사용하여 구성된다. 특히 VCO는 N-위상 클록을 위해 N개의 지연 소자로 구성된다. DLL구조는 위상 여유가 항상 확보되어 있기 때문에 절대적으로 안정하지만 주파수 체배가 안되기 때문에 고속 클록을 출력하기 어렵다. 하지만 PLL 구조는 체배가 가능하여 고속 클록을 출력할 수 있지만 안정성 문제가 있기 때문에 안정성을 고려한 설계가 요구된다. 이와 같은 다중-위상 클록 발생기는 용도에 따라서 다양하게 사용되어 지고 있다[4-6].

그림 6(a)는 같이 다중-위상 DLL의 PD 또는 CP에 공정 변화 등에 의해서 오프셋이 발생했을 때 VCDL의 전체 지연이 변화되면서 모든 위상에 α의 위상 오차가 발생된 것이다. ΦN-1에는 오프셋만큼의 위상 오차가 추가로 발생된다. 이때 Δt와 α는 식 (1)과 같이 정의 된다. 그리고 VCDL 구조로 인하여 위상이 증가될수록 최대 지터가 증가되어 전체 성능을 악화 시킨다. 하지만 그림 6(b)와 같이 다중-위상 PLL은 PFD 또는 CP에 오프셋이 발생해도 PLL 구조적 특징에 의해 추가적인 위상 오차가 발생되지 않는다. 그리고 링 구조를 가진 VCO에 의해서 위상이 증가해도 일정한 지터를 가진다.

DLL의 최대 지터는 N이 증가될수록 증가되며 위상 오차는 오프셋에 의해서 증가된다[7]. 반면 PLL은 일정한 지터를 가지며 오프셋에 의한 위상 오차가 발생되지 않는다. 본 논문에서는 빠른 고정 시간과 작은 지터를 가지는 주파수 합성기를 위한 51-위상 출력 클록을 가지는 CMOS PLL을 제안한다.

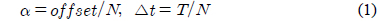

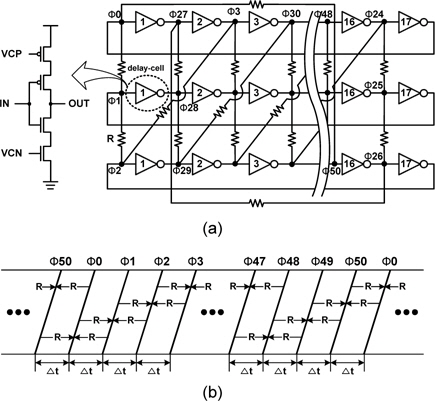

그림 7은 제안된 51-위상 출력 클록을 가지는 PLL블록도이다. 제안된 PLL은 VCO 지연 소자를 제어하기 위한 VCN과 VCP를 출력하는 바이어스 발생기[8][9]와 51-위상 클록을 출력하기 위해 51개의 지연 소자로 구성된 VCO로 구성된다. 그리고 일반적인 PFD, CP, 루프 필터를 사용한다. 제안된 PLL은 PFD에 의해서 VCO의 출력 클록과 CLK_REF의 위상과 주파수를 비교하여 CP를 통해 VCTRL을 업데이트시켜 VCO의 출력 클록을 고정시키는 기본적인 PLL과 동일한 동작을 수행한다. 그리고 고정 상태가 되면 일정한 위상차를 가지는 51-위상 클록을 출력한다.

최대 동작 주파수 생성을 위한 PLL에서는 다수개의 VCO를 사용하며 주로 위상 커플러를 이용하여 이를 결합시켰다[10-12]. 위상 커플러는 인접한 위상들이 일정한 위상관계를 형성할 수 있도록 제어해주는 역할을 한다. 이러한 위상 커플러는 지연 소자 보다 작은 지연을 가지면서 위상 클록의 위상을 제어하기 때문에 지연 소자를 이용한 커플링보다 더 높은 동작 주파수를 출력할 수 있다. 이와 같은 위상 커플러는 상승과 하강 엣지를 지속적으로 제어 하면서 위상을 고정 시키기 때문에 제어 되는 동안 지터와 위상 오차 특성을 악화 시킨다.

그림 8(a)는 제안된 커플링 구조를 가진 VCO의 블록도이다. 각각의 지연 소자는 전류 제한 인버터 구조로 바이어스 발생기로부터 출력되는 VCN, VCP에 의해서 VCO 주파수가 제어 된다. VCO의 최대 동작 주파수 확보를 위해 51개의 지연 소자들을 단일 링으로 구현하지 않고 17개씩 3개의 링으로 구현한다. 각 링은 17개의 동일한 위상차를 가진 위상 클록을 출력하지만 3개의 링사이에는 일정한 위상 관계가 성립되지 않기 때문에 기존의 위상 커플러와 같은 역할을 하는 저항을 사용한다. 각 위상 클록은 저항으로 연결되어 그림 8(b)와 같이 일정한 위상 관계를 형성하고 동시에 저항 평준화에 의해서 위상 오차 감소시킨다. 예로 Φ1은 저항으로 연결된 Φ0와 Φ2에 의해서 일정한 위상 관계가 성립되는 동시에 Φ0와 Φ2의 위상 관계에 동일한 영향을 준다. 이와 같이 저항에 의해서 인접한 위상 클록 간에는 식 (2)의 Δt가 형성된다. 이와 같은 역할을 하는 저항의 크기는 위상 오차와 지터를 고려하여 결정하여야 한다. 저항이 크면 평준화가 감소되어 위상 오차가 증가되고 저항이 작으면 위상 클록간의 간섭으로 인해 상승과 하강 시간이 증가되어 지터가 악화된다. 즉, 저항의 크기는 위상 오차와 지터 특성 사이에 트레이드오프 관계를 가진다.

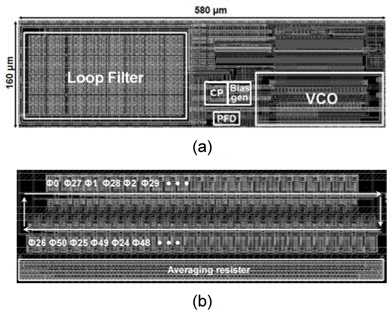

51-위상 출력 클록을 가지는 PLL은 65 nm 1-폴리 9-메탈 CMOS 공정에서 1.0 V 공급 전압으로 설계되었다. 측정된 동작 주파수 범위는 15 ~ 210 MHz이며 면적은 그림 9(a)의 레이아웃과 같이 580 × 160 μm2이다. 그리고 전력 소모는 3.48 mW이다.

그림 9(b)는 배선 부정합으로부터 발생되는 추가적인 위상 오차를 감소시키기 위해 일정한 간격으로 지연 소자를 배치한 VCO 레이아웃이다.

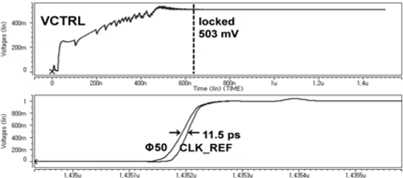

그림 10은 125 MHz에서 시뮬레이션된 전체 회로의 VCTRL 타이밍도와 고정 상태에서의 Φ50과 CLK_REF 의 위상 오차이다. VCTRL은 약 630 ns에서 고정 상태가 되고 전압은 503 mV를 가진다. 고정 상태에서 Φ50과 CLK_REF의 위상 오차는 11.5 ps이다.

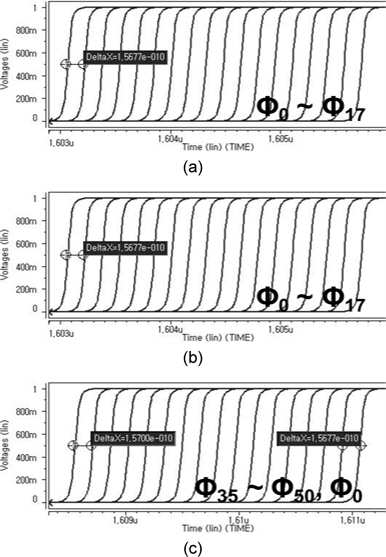

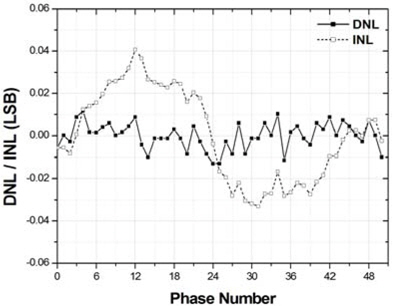

그림 11(a), (b), 그리고 (c)는 125 MHz에서 시뮬레이션된 51-위상 클록의 파형으로 모든 위상 클록의 위상차가 비교적 일정한 간격을 가진다. 그림 12은 51-위상 클록의 차동 비선형성(DNL)과 적분 비선형성(INL)로 각 위상 클록의 위상 오차를 보여준다. 시뮬레이션된 DNL과 INL은 각각 −0.013/+0.012 LSB와 ‒0.033/ +0.041 LSB이다. DNL 결과로부터 최대 위상 오차는 2.04 ps이고 그림 11의 Φ50과 CLK_REF의 위상 오차는 11.5 ps이다. 즉, PFD 또는 CP 부정합으로 인한 위상 오차는 51-위상 클록의 위상 오차에 영향을 주지 않는다.

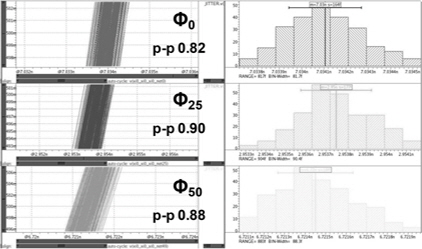

그림 13는 125 MHz에서 시뮬레이션된 Φ0, Φ25, Φ50 peak-to-peak 지터로 각각 0.82 ps, 0.90 ps, 0.88 ps이다. 시뮬레이션된 지터는 VCO구조로 인하여 비교적 일정한 수치를 가진다. 표 1은 본 논문에서 제안된 다중-위상 출력 클록을 가지는 PLL의 성능 요약이다.

성능 요약

본 논문에서는 다중-위상 클록 발생기 기반의 주파수 합성기에 사용될 수 있는 51-위상 출력 클록을 가지는 CMOS PLL을 제안한다. 다중-위상 PLL 구조는 위상이 증가해도 일정한 지터를 가지며 PFD 또는 CP에 오프셋이 발생해도 추가적인 위상 오차가 발생하지 않기 때문에 다중-위상 DLL 구조보다 최대 지터와 DNL을 개선할 수 있다. 그러므로 다중-위상 PLL 구조가 DLL 구조보다 주파수 합성기에 더 적합하다. 제안된 51-위상 출력 클록을 가지는 PLL은 최대 동작 주파수 확보를 위해 커플링 구조인 VCO를 사용한다. VCO는 17단의 지연소자로 구성된 3개의 VCO와 위상 클록 사이에 연결된 저항으로 구성된다. 저항은 3개의 VCO의 위상을 고정 시켜주며 동시에 위상 평준화 역할을 하여 위상 오차를 개선한다. 15 ~ 210 MHz 동작 주파수 범위를 가지는 51-위상 출력 클록을 가지는 PLL은 1.0 V 공급전압에서 65 nm 1-폴리 9-메탈 CMOS 공정을 이용하여 설계되었다. 125 MHz에서 시뮬레이션된 출력 클록의 peak-to-peak 지터는 0.82 ps이다. 그리고 DNL과 INL은 각각 −0.013/+0.012 LSB와 −0.033/+0.041 LSB이다. 면적과 전력 소모는 각각 580 × 160 μm2과 3.48mW이다.