Asymmetric double gate(DG) MOSFET is a novel transistor to be able to reduce the short channel effects. This paper has analyzed a off current for conduction path of asymmetric DGMOSFET. The conduction path is a average distance from top gate the movement of carrier in channel happens, and a factor to change for oxide thickness of asymmetric DGMOSFET to be able to fabricate differently top and bottom gate oxide thickness, and influenced on off current for top gate voltage. As the conduction path is obtained and off current is calculated for top gate voltage, it is analyzed how conduction path influences on off current with parameters of oxide thickness and channel length. The analytical potential distribution of series form is derived from Poisson’s equation to obtain off current. As a result, off current is greatly changed for conduction path, and we know threshold voltage and subthreshold swing are changed for this reasons

트랜지스터의 미세화는 집적회로 개발에 가장 중요한 요소이다. 가장 광범위하게 사용되고 있는 CMOS 트랜지스터의 경우 20nm 이하로 미세화 할 경우, 단채널 효과로 알려진 문턱전압이하 스윙 특성저하, 문턱전압 이동현상 등 트랜지스터 동작에 심각한 영향을 나타내고 있다. 이러한 문제점을 해결하기 위하여 개발되고 있는 소자가 다중게이트 MOSFET이다. 다중게이트 MOSFET는 하나의 게이트를 갖는 CMOSFET와 달리 채널주위에 2개 이상의 게이트를 형성하여 게이트 단자에 의한 채널 내 캐리어의 제어능력을 단자 개수만큼 향상시킬 수 있다는 장점이 있다. 그러므로 제작공정상가능하다면 여러 개의 게이트 단자를 채널주변에 제작하여 사용하려는 노력을 하고 있다. 이에 부응하기 위하여 개발되고 있는 소자가 FinFET와 이중게이트 MOSFET 그리고 원통형 MOSFET이다[1-3]. FinFET의 경우 좁고 높은 지느러미 형태로 채널을 형성하여 주변을 게이트 단자로 감싸 제작한 트랜지스터로써 지느러미 형태의 핀을 제작하는데 어려움을 겪고 있다. 원통형 MOSFET는 아직 연구 단계로써 채널을 원통 형태로 제작하고 아래는 소스 위는 드레인을 제작하며 원통주위를 게이트 단자로 제작하는 트랜지스터이다. 이중게이트 MOSFET는 상단과 하단에 두 개의 게이트 단자를 제작하여 채널 내 전하를 제어하는 트랜지스터로써 가장 광범위하게 연구되고 있다. 이중게이트 구조는 SOI기술의 발달과 함께 발전하고 있으며 가장 간단한 구조의 다중게이트 MOSFET로써 대칭형 구조와 비대칭형 구조로 구분된다.

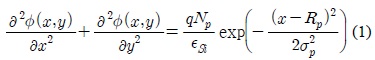

대칭형 이중게이트 MOSFET는 상단과 하단의 게이트 산화막 두께를 동일하게 제작하고 상단과 하단의 게이트 단자를 묶어 동일한 전압을 인가하는 구조이다. 이에 반해 비대칭 이중게이트 MOSFET는 상단과 하단의 게이트 산화막 두께를 달리 제작할 수 있으며 상단과 하단의 게이트 단자에 각각 별도의 전압을 인가할 수 있다. 비대칭 이중게이트 MOSFET의 경우, 소스, 드레인, 상단 게이트, 하단 게이트 단자로 이루어진 4단자로써 상단과 하단의 게이트 산화막 두께 등, 단채널 효과를 제어할 수 있는 요소가 증가하여 효율적으로 단채널 효과를 감소시킬 수 있다는 장점을 갖는다. 이에 본 연구에서는 비대칭 이중게이트 MOSFET의 상·하단 게이트 산화막 두께 및 채널길이 등이 차단전류에 미치는 영향을 관찰하고자한다. 특히 대부분의 전류가 흐르는 전도중심의 변화가 차단전류에 미치는 영향을 고찰함으로써 게이트전압변화가 전도중심에 미치는 영향과 차단전류의 관계를 관찰할 것이다. 이를 위하여 급수형태의 해석학적 전위분포를 포아송방정식을 풀어 구하였으며 전위분포모델을 이용하여 차단전류모델을 구하였다. Ding 등의 모델[4]과 달리 전하분포모델은 가우스분포함수를 사용하였다.

2장에서는 포아송방정식의 해석학적 전위모델 및 차단전류모델에 대하여 설명할 것이며 3장에서 이 모델을 이용하여 구한 전도중심 및 차단전류를 산화막 두께 및 채널길이에 따라 고찰하였다. 또한 4장에서 결론을 맺을 것이다.

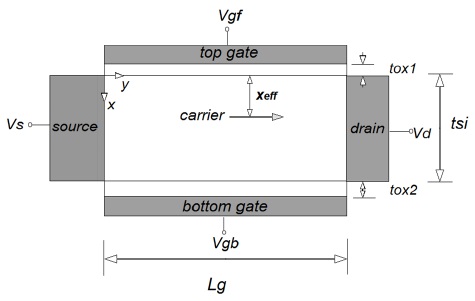

비대칭 이중게이트 MOSFET의 개략도를 그림 1에 도시하였다. 상·하단 게이트 단자에 각각

여기서

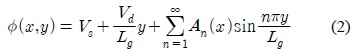

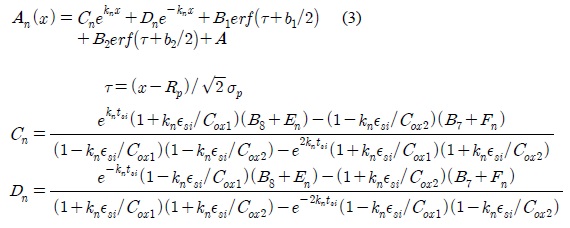

Ding 등의 경계조건을 이용하여 식 (1)을 풀면 다음과 같은 급수형태의 전위분포를 구할 수 있다[4].

이며 여기서

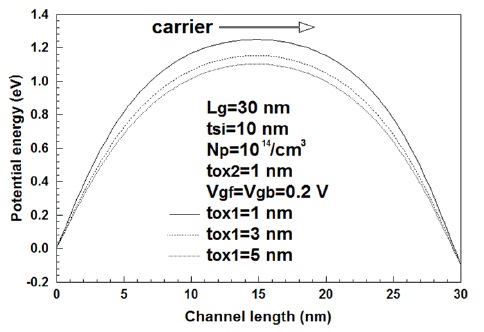

식 (2)와 식 (3)에서 알 수 있듯이 전위분포는 산화막 두께에 따라 변화할 것이며 이에 따른 에너지장벽의 변화를 그림 2에 도시하였다. 그림 2에서 알 수 있듯이 에너지장벽의 높이는 상단 및 하단의 게이트 산화막 두께에 따라 변화하므로 차단전류 역시 두 요소에 따라 변화할 것이다.

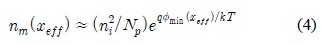

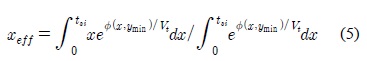

그림 2에서 에너지 장벽을 넘어 전도중심에서 이동하는 전자의 농도는 볼츠만통계를 이용하면 다음과 같이 구할 수 있다.

여기서

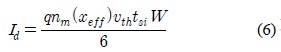

일정치 않게 운동하는 전자들의 1/6이 소스에서 드레인으로 향할 것이며 단위시간당

이다.

이상과 같이 식 (2)의 전위분포는 상하단의 게이트 산화막 두께에 의하여 변화할 것이며 차단전류는 식 (6)에서 알 수 있듯이 전자농도에 따라 변화하며 이는 전위분포 및 전도중심에 따라 변화하므로 결국 차단전류는 상·하단 게이트 산화막 두께 및 전도중심 등에 따라 변화할 것이다. 그러므로 본 연구에서는 상단과 하단의 게이트 산화막 두께를 파라미터로 하여 전도중심이 차단전류에 미치는 영향을 고찰할 것이며 비대칭 이중게이트 MOSFET의 채널길이가 단채널 효과에 미치는 영향을 관찰할 것이다.

본 연구에서 제시한 차단전류 모델의 타당성은 참고문헌[6]에서 이미 입증하였으므로 이 모델을 사용하여 상단 및 하단 게이트 산화막 두께 그리고 채널길이에 대한 차단전류의 변화를 고찰할 것이다.

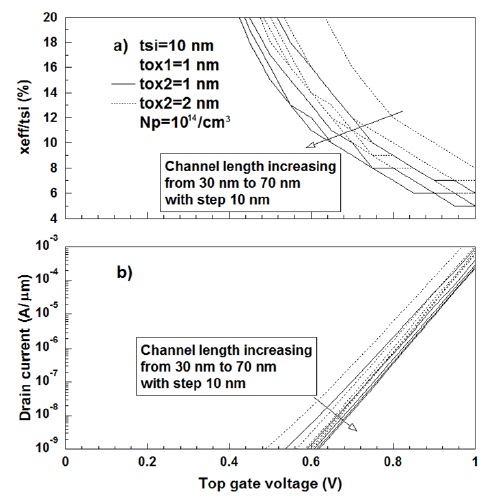

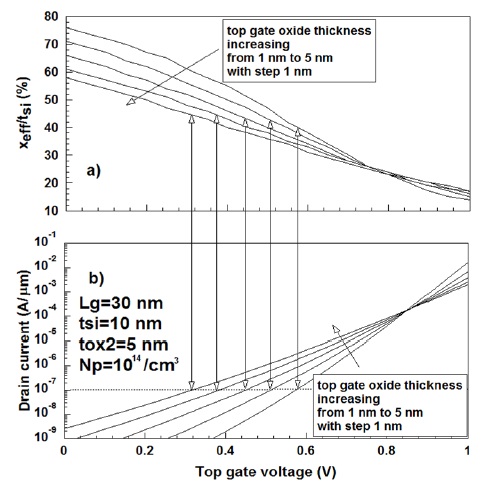

채널길이 및 하단게이트 산화막 두께를 파라미터로 하여 상단게이트 전압의 변화에 따른 전도중심 및 차단전류의 변화를 그림 3에 도시하였다. 그림 3a)에서 알 수 있듯이 하단게이트 산화막 두께가 증가할수록 전도 중심은 내부로 이동하며 차단전류도 증가하는 것을 관찰할 수 있다. 또한 상단게이트 전압이 증가할수록 전도중심이 상단게이트 단자로 이동하는 것을 알 수 있다. 채널길이에 따라 분석해 보면, 채널길이가 증가할수록 전도중심은 상단 게이트단자로 이동하고 차단전류도 감소하고 있다는 것을 관찰할 수 있다. 이와 같이 전도중심과 차단전류는 상호관계가 존재하며 이는 산화막 두께에 따라 민감하게 변화한다는 것을 알 수 있다. 차단전류의 변화는 문턱전압이동현상이나 문턱전압이하 스윙 값의 저하 현상 등 단채널 효과를 나타내므로 이에 대하여 상세히 고찰할 것이다.

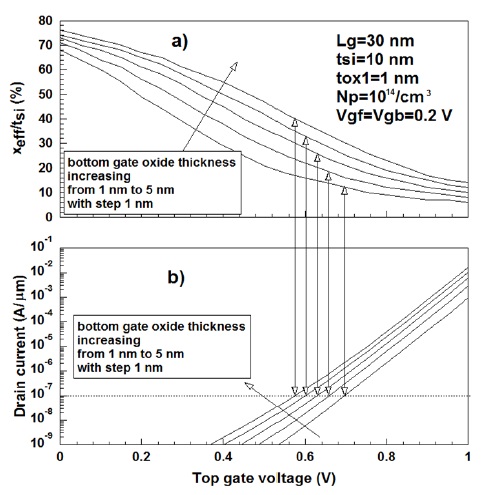

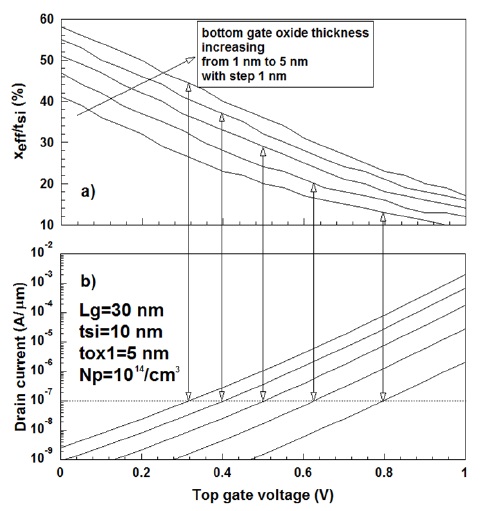

먼저 하단게이트 산화막 두께의 변화에 대한 전도 중심 및 차단전류의 변화를 그림 4에 도시하였다. 차단전류가 0.1㎂/㎛ 일 때 상단게이트 전압을 문턱전압으로 정의[7]함으로써 전도중심과 문턱전압의 변화를 함께 도시하였다.

산화막 두께만의 효과를 관찰하기 위하여 상·하단게이트 전압은 동일하게 유지하였다.

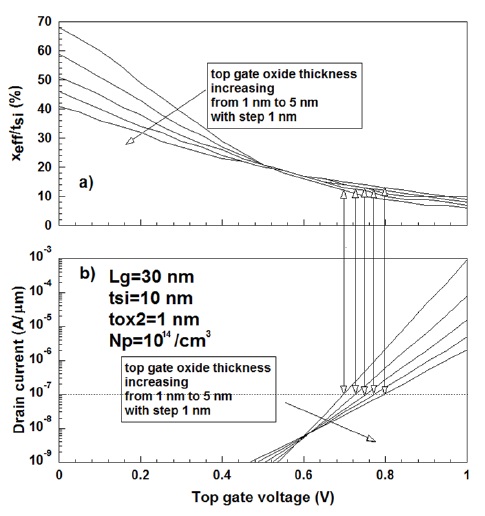

상단 게이트 산화막 두께 변화에 따른 전도중심 및 차단전류의 변화를 관찰하기 위하여

그림 6과 그림 7을 비교해 보면

비대칭 이중게이트 MOSFET의 전도중심에 따른 차단전류를 분석하였다. 상단 게이트 전압에 따른 차단전류의 변화는 문턱전압이하 스윙 및 문턱전압의 변화를 구할 수 있는 기초자료이다. 상·하단 게이트 산화막 두께를 달리 제작할 수 있는 비대칭 DGMOSFET에서 산화막 두께에 따라 차단전류는 영향을 받고 있었으며 전도중심도 변화하였다. 특히 상단 게이트 산화막 두께와 하단 게이트 산화막 두께의 크기에 따라 전도중심 및 차단전류가 변하였으며 변화하는 경향도 큰 차이를 보였다. 상단게이트 산화막 두께의 변화는 전도중심에 큰 영향을 미치지 않았으나 전도중심의 약간의 변화에도 문턱전압이하 스윙은 크게 변화하는 것을 알 수 있었다. 하단 게이트 산화막 두께의 변화는 문턱전압이하 스윙보다 문턱전압의 변화에 더 큰 영향을 미치고 있었다. 이와 같은 결과는 비대칭 이중게이트 MOSFET의 개발에 기초자료로 사용될 수 있을 것이다.