This paper describes an efficient hardware implementation of lightweight encryption algorithm LEA-128/192/256 which supports for three master key lengths of 128/192/256-bit. To achieve area-efficient and low-power implementation of LEA crypto- processor, the key scheduler block is optimized to share hardware resources for encryption/decryption key scheduling of three master key lengths. In addition, a parallel register structure and novel operating scheme for key scheduler is devised to reduce clock cycles required for key scheduling, which results in an increase of encryption/decryption speed by 20~30%. The designed LEA crypto-processor has been verified by FPGA implementation. The estimated performances according to master key lengths of 128/192/256-bit are 181/162/109 Mbps, respectively, at 113 MHz clock frequency.

다양한 기기들이 인터넷에 연결되어 인간의 조작이나 도움 없이 서로 정보를 교환하고 공유하는 사물인터넷(IoT: Internet of Things) 기술이 빠른 속도로 실용화 되고 있으며, 스마트 홈, 스마트 보안, 지능형 교통정보 시스템 등 다양한 분야에 폭 넓게 적용되고 있다. IoT는 복잡하고 이질적인 네트워크에서 다양한 형태의 데이터를 처리하고 전송하므로, 해커나 악의적인 소프트웨어, 바이러스 등에 의해 정보가 유출, 조작, 변조되는 정보보안 위험에 노출될 수 있다. IoT 보안은 센서 네트워크, 인터넷과 유사한 보안 이슈를 가지며 프라이버시, 인증 및 접속 제어, 정보 저장 및 관리 등의 정보보안 이슈들을 포함한다[1,2].

정보보안을 위해 사용되는 대표적인 기술이 암호이다. 암호(Cryptography)는 그리스어에서 기원한 용어로서 비밀기록(secret writing)을 의미하지만, 오늘날에는 다양한 형태의 보안 공격에 안전하도록 정보를 변형하는 기술을 뜻한다. 암호화는 컴퓨터에 저장되어 있거나 네트워크를 통해 전달되는 정보를 제삼자가 가로채어 그 내용을 노출시키거나 의도적으로 조작하는 보안공격으로부터 정보를 보호하기 위한 수단으로 사용되며, IoT 시스템을 구현하는 핵심 기술 요소 중 하나로 평가되고 있다. IoT 보안을 위해서는 기존의 유무선 인터넷 보안과 동일한 대칭키 블록암호 방식과 공개키 암호 방식이 사용된다. 센서 네트워크, RFID 태그, 스마트카드 등 하드웨어/소프트웨어 자원이 제한되는 IoT 네트워크와 단말기의 보안을 위해서는 저전력, 작은 하드웨어/소프트웨어 자원을 소모하는 경량 암호(lightweight cryptography) 알고리듬의 사용이 요구된다[3]. 최근에는 IoT 보안에 적합도록 개발된 HIGHT(HIGh security and light weigHT) [4], LEA (Lightweight Encryption Algorithm) [5], CLEFIA [6], PRESENT [7], mCrypton [8], TEA (Tiny Encryption Algorithm) [9] 등 다양한 경량 블록암호 방식들이 제안되고 있다.

보안 알고리듬은 소프트웨어 또는 하드웨어로 구현되며, 물리적인 안전성과 저전력 소모가 중요한 시스템에서는 전용 하드웨어 구현 방식이 사용된다. 최근에는 IoT, 스마트카드, NFC 보안을 위한 저전력/저면적 하드웨어 구현 결과들이 발표되고 있다[10,11].

본 논문에서는 국가보안기술연구소(NSRI)에서 개발한 128비트 블록암호 알고리듬 LEA를 IoT 환경에 적합하도록 최적화한 LEA 프로세서를 설계하고, FPGA 구현을 통해 하드웨어 동작을 검증하였다. Ⅱ장에서는 블록암호 알고리듬 LEA에 대해 간략히 설명하고, Ⅲ장에서는 LEA-128/192/256 암호/복호 프로세서 설계에 대해 설명한다. 설계된 회로의 기능 검증 및 FPGA 구현에 대해 Ⅳ장에서 기술하며, Ⅴ장에서 결론을 맺는다.

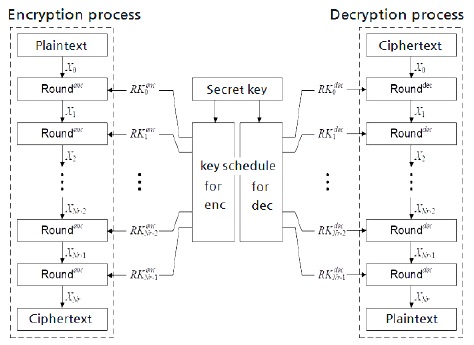

블록암호 LEA는 128비트의 평문/암호문 블록을 128/192/256비트의 마스터키로 암호화/복호화하여 128비트의 암호문/평문을 생성하는 대칭키 방식의 암호 알고리듬이다. LEA는 ARX(Addition, Rotation, XOR) 연산을 기반으로 한 Feistel 유사 구조이며, 마스터키의 길이에 따라 24/28/32 라운드의 연산을 통해 암호화/복호화가 이루어진다. 128/192/256비트의 마스터키로부터 생성되는 192비트의 라운드 키가 라운드 변환에 사용된다. 라운드 함수는 32비트 단위의 ARX 연산으로 구성되어 이들 연산을 지원하는 범용 32비트 소프트웨어 플랫폼에서 고속으로 동작한다. 또한 라운드 함수 내부의 ARX 연산 배치는 충분한 안전성을 보장함과 동시에 S-box의 사용을 배제하여 경량 구현이 가능하도록 한다. LEA의 암호화 및 복호화 과정은 그림 1과 같으며, 라운드 키를 생성하는 키 스케줄러와 암호화/복호화를 수행하는 라운드 함수로 구성된다.

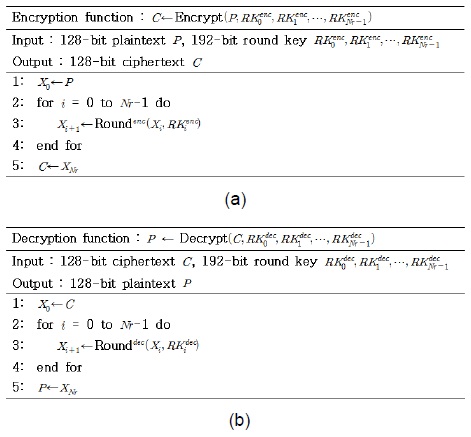

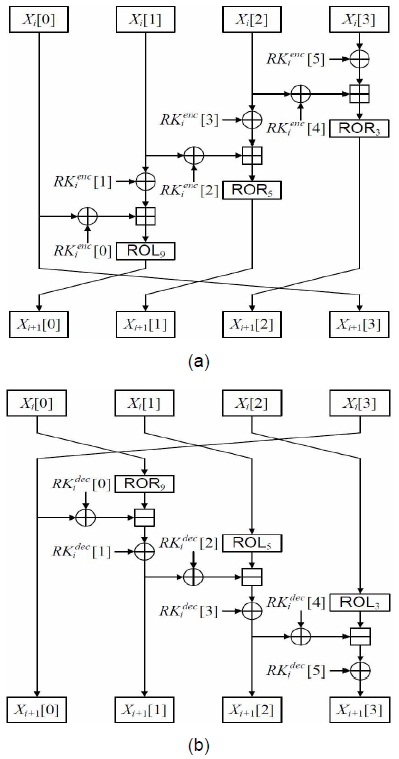

암호화 과정과 복호화 과정은 서로 역순으로 이루어지며, 암호화 과정에서의 모듈로 가산은 복호화 과정에서 모듈로 감산으로 구현되고, 순환이동도 반대방향으로 이루어진다. 암호화 과정은 비밀키

암호화 과정의

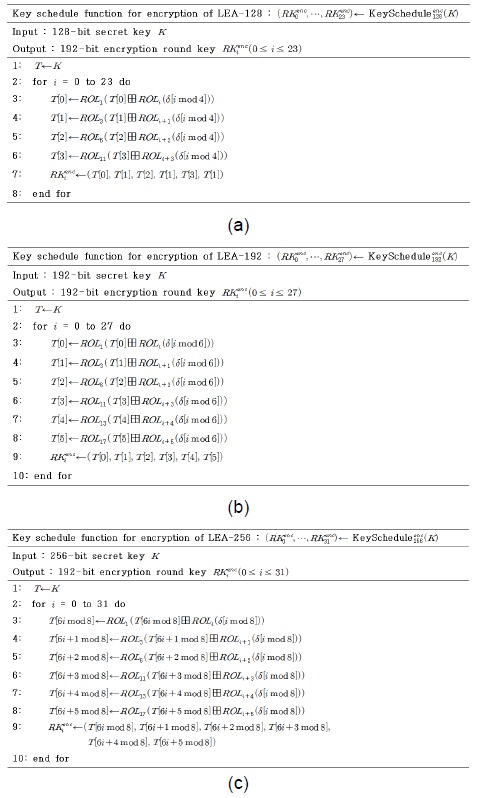

마스터키 길이에 따라 생성되는 상수의 개수가 달라 지며, 암호화/복호화에 따라 AR 연산의 순서가 반대로 적용된다. 암호화 키 스케줄링은 마스터키

복호화 라운드 키는 의 관계를 제외하면 암호화 키 생성과 동일한 방법으로 생성된다. LEA- 128/192/256의 암호화 키 스케줄 함수의 슈도 코드는 그림 4와 같다.

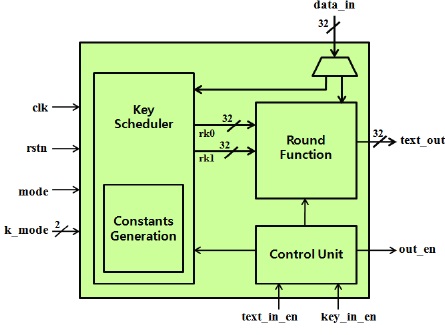

본 논문에서는 128비트의 평문/암호문 블록을 128/192/256비트의 마스터키로 암호화/복호화하여 128비트의 암호문/평문을 생성하는 LEA 암호/복호 프로세서 를 설계하였다. 설계된 LEA 코어의 전체 구조는 그림 5와 같으며, 라운드 블록, 키 스케줄링 블록, 제어 블록으로 구성된다. 라운드 블록은 마스터키 길이 128/192/256비트에 따라 24/28/32번의 라운드 변환을 통해 암호/복호 연산을 수행하며, 키 스케줄링 블록은 각 라운드 연산에 사용되는 192비트의 라운드 키를 on-the-fly 방식으로 생성한다. 저면적 구현을 위해 라운드 블록을 32비트 회로로 설계하였으며, 입력 핀(data_in)을 공유하여 마스터키와 평문/암호문이 시분할 방식으로 입력되도록 하였다. 또한, 마스터키의 길이에 따른 3가지 모드와 암호화/복호화 연산의 하드웨어 자원이 공유되도록 설계하였다.

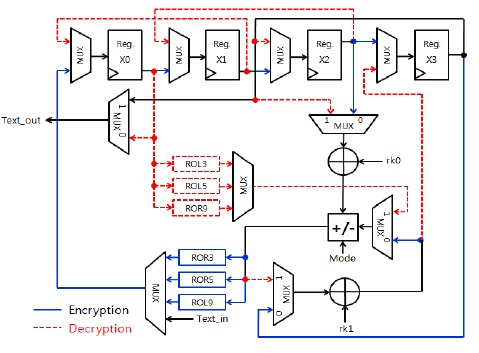

라운드 블록은 128비트의 평문/암호문과 키 스케줄러에 의해 생성되는 192비트의 라운드 키를 입력받아 라운드 연산을 반복적으로 처리하여 암호/복호 연산을 수행한다. 라운드 블록은 그림 6과 같이 4개의 32비트 레지스터(

Text_in 포트를 통해 입력되는 128비트의 평문/암호문은 32비트 단위로 4클록 주기에 걸쳐 상태변수 레지스터

128비트 평문/암호문의 최상위 32비트가 레지스터

가) 암호화 모드 동작

키 스케줄링 블록에서 생성된 라운드 키 rk0와 레지스터

나) 복호화 모드 동작

복호화 모드에서는 암호화 모드와 반대의 순서로 라운드 키가 사용된다. 암호화 과정의 XOR→Addition→Rotation의 연산 순서는 복호화 과정에서는 Rotation→Subtraction→XOR의 순서로 적용된다. 비트 순환이동도 반대 방향으로 이루어지며, 32비트 modulo 가산은 감산으로 대체된다. 또한, 내부 레지스터의 데이터 이동방향도

암호/복호 라운드 연산에 사용되는 192비트의 라운드 키는 키 스케줄링 알고리듬에 의해 생성된다.

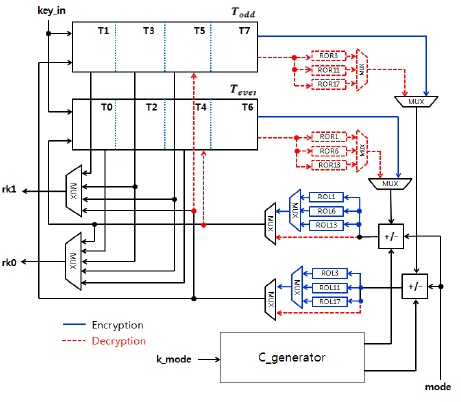

본 논문에서 설계된 키 스케줄링 블록은 그림 7과 같으며, 8개의 32비트 내부 레지스터(

키 스케줄링 블록은 마스터키의 길이(128/192/256비트)와 암호화/복호화 동작모드에 따라 회로의 동작이 달라진다. 신호 mode=0일 때 암호화 키 스케줄링이 이루어지고, mode=1일 때 복호화 키 스케줄링이 이루어 진다. 마스터키의 길이를 지정하는 2비트의 신호 k_mode에 따라 멀티플렉서(MUX)의 동작이 제어되어 LEA-128, LEA-192, LEA-256 모드의 키 스케줄링이 선택적으로 수행된다. 레지스터(

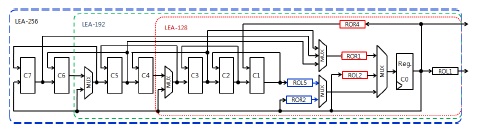

본 논문에서는 그림 7과 같이 32비트 레지스터 8개 (

LEA-128 모드는 32비트 레지스터 4개를 사용하여 4클록 주기로 구현이 가능하지만, 32비트 레지스터 6개를 사용하여 생성된 키를 저장하고 멀티플렉서를 통해 출력하는 방법을 적용하였다. 본 논문의 방법은 라운드키 생성에 3클록 주기가 소요되며, 키 스케줄링에 소요되는 클록 주기를 감소시킬 수 있다. 한편, 문헌 [12]의 방법에서는 라운드 키 생성에 4클록 주기가 소요된다. LEA-256 모드의 동작에서는 해당 라운드의 키 스케줄링에 사용되지 않는 중간 변환 값이 레지스터

그림 9는 본 논문에서 제안한 방법(그림 7)과 문헌[12]의 방법에 의한 키 스케줄링의 라운드 연산에 소요되는 클록 수를 비교한 것이다. 그림 9-(a),(b)는 마스터 키가 128-비트인 LEA-128 모드의 동작을 보이고 있다. 문헌 [12]의 방식은 라운드 당 4클록 주기가 필요한 반면에, 본 논문의 방식은 라운드 당 3클록 주기가 소요되어 암호 연산에 20%, 복호 연산에 23%의 속도 개선이 얻어진다. 그림 9-(c),(d)는 마스터키가 256-비트인 LEA-256 모드의 동작을 보이고 있다. 문헌 [12]의 방식은 라운드 당 6클록 주기가 필요한 반면에, 본 논문의 방식은 라운드 당 4클록 주기가 소요되어 암호 연산에 약 33%, 복호 연산에 32%의 속도 개선이 얻어진다.

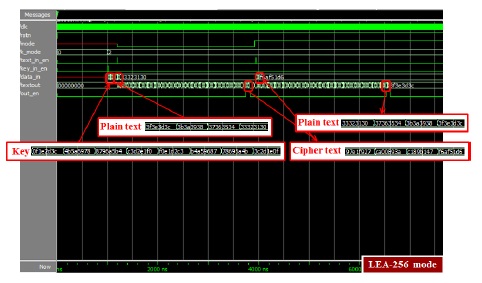

Verilog HDL로 설계된 LEA 코어의 기능검증 결과는 그림 10과 같으며, 128비트의 평문 “30313233 34353637 38393a3b 3c3d3e3f”와 256비트의 마스터키 “0f1e2d3c 4b5a6978 8796a5b4 c3d2e1f0 f0e1d2c3 b4a59687 78695a4b 3c2d1e9f”를 사용한 시뮬레이션 결과를 보이고 있다. 암호화 결과로 암호문 “f6af51d6 c189b147 ca00893a 97e1f927”이 출력되었고, 이를 다시 복호화하여 평문 “30313233 34353637 38393a3b 3c3d3e3f”이 출력되었으며, 설계된 LEA 프로세서의 논리기능이 정상 동작함을 확인하였다.

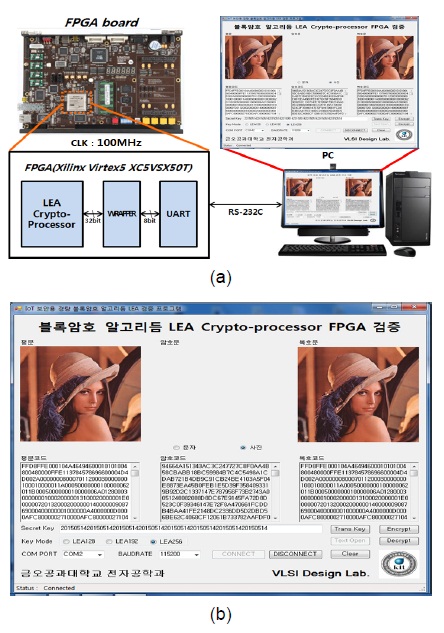

기능검증이 완료된 LEA 코어는 FPGA 구현을 통해 하드웨어 동작을 검증하였다. 그림 11(a)는 FPGA 보드, UART 인터페이스, 구동 소프트웨어로 구성된 검증시스템 구성도이며, Xilinx Virtex5 XC5VSX-50T 디바이스가 사용되었다. PC에서 입력된 비밀키와 평문/암호문 데이터가 RS232C 통신을 통해 FPGA로 입력되고, FPGA에서 출력되는 암호문/평문 데이터가 표시된다.

그림 11(b)는 FPGA 검증 결과를 보이고 있다. 평문을 암호화하고, 암호문을 복호화하여 원래의 평문과 일치하는 복호결과가 출력되어 FPGA에 구현된 LEA 프로세서가 올바르게 동작함을 확인하였다. 설계된 LEA 프로세서는 FPGA 합성 결과 2,364 슬라이스로 구현되었다. FPGA에서 최대 113 MHz 클록 주파수로 동작할 때, 128/192/256비트의 마스터키 길이에 따른 암호화 동작 시 각각 181/162/109 Mbps, 복호화 동작 시 각각 188/162/109 Mbps의 성능을 갖는 것으로 평가되었다.

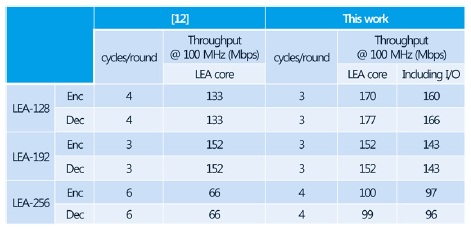

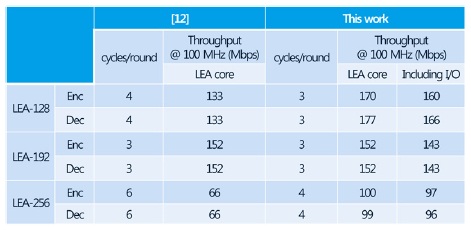

표 1은 본 논문에서 설계된 LEA 코어와 문헌 [12]에 발표된 사례의 성능 비교를 보이고 있다. 문헌 [12]의 LEA 코어는 단일 마스터키 길이만 지원하는 반면에 본 논문의 설계는 세 가지 키 길이를 동시에 지원하므로, 하드웨어 복잡도에 대한 직접적인 비교는 어렵다. 100 MHz 클록으로 동작하는 경우에, 본 논문의 LEA 코어는 99~177 Mbps의 출력율을 가져 문헌 [12]의 LEA 코어에 비해 30% 정도 높은 성능을 갖는 것으로 평가되었다.

LEA 코어의 비교

본 논문에서는 한국정보통신기술협회(TTA) 표준으로 등록된 128비트 블록암호 알고리듬 LEA-128/192/256을 하드웨어로 구현하여 동작을 확인하였다. 마스터키 길이에 따른 3가지 동작모드와 암호/복호 연산의 하드웨어 자원이 공유되도록 최적화하여 설계하였다. 키 스케줄러의 구조와 동작방식을 개선하여 암호/복호 동작속도를 20~30% 향상시켰다. 설계된 LEA 프로세서는 Xilinx Vertex5 FPGA에서 최대 113 MHz 클록으로 동작 가능하며, 마스터키 길이 128/192/256-비트 모드에서 각각 181/162/109 Mbps의 성능을 갖는 것으로 평가 되었다. 설계된 LEA-128/192/256 암호/복호 프로세서는 IoT 및 모바일 기기 보안 등과 같이 저전력과 경량화가 요구되는 응용분야의 보안 IP로 활용이 가능하다.

![키 스케줄링 및 라운드 변환의 동작 타이밍 (a) 문헌[12]의 LEA-128 모드의 키 스케줄링 (b) LEA-128 모드의 제안된 키 스케줄링 (c) 문헌 [12]의 LEA-256 모드의 키 스케줄링 (d) LEA-256 모드의 제안된 키 스케줄링](http://oak.go.kr/repository/journal/17275/HOJBC0_2015_v19n7_1608_f009.jpg)