This paper describes an efficient hardware design of Lightweight Encryption Algorithm (LEA) developed by National Security Research Institute(NSRI). The LEA crypto-processor supports for master key of 128-bit. To achieve small-area and low-power implementation, an efficient hardware sharing is employed, which shares hardware resources for encryption and decryption in round transformation block and key scheduler. The designed LEA crypto-processor was verified by FPGA implementation. The LEA core synthesized with Xilinx ISE has 1,498 slice elements, and the estimated throughput is 216.24 Mbps with 135.15 MHz.

정보통신 기술의 비약적인 발달은 오늘날 우리 주변의 사물들을 네트워크로 연결시켜 주고 이들에 대한 정보를 언제, 어디서나 쉽게 접할 수 있는 사물인터넷(IoT: Internet of Things) 시대의 도래를 촉진하고 있다. IoT 서비스는 스마트기기, 센서 등 다양한 단말 및 이종 네트워크, 애플리케이션 등을 활용하므로, 발생할 수 있는 보안 위협도 많을 것으로 예상된다[1].

오늘날 널리 알려져 있는 정보보안 기술 중 하나가 암호이며, 그리스어에서 기원한 암호(Cryptography)라는 용어는 ‘비밀기록(secret writing)’을 의미하지만 현재는 ‘메시지가 공격에 안전하도록 메시지 변형을 하는 예술과 과학’을 뜻한다. 과거에는 암호가 단지 비밀 키를 이용하여 메시지의 암호화와 복호화를 하는 것으로 간주되었지만, 오늘날 암호는 세 개의 별개의 메커니즘, 즉 공개키 암호화, 비밀 키 암호화, 해슁(Hashing)으로 정의된다. 암호화는 컴퓨터에 저장되어 있거나 네트워크를 통해 전달되는 정보를 제삼자가 가로채어 그 내용을 노출시키거나 의도적으로 내용을 조작·변경하는 등의 보안공격으로부터 정보를 보호하기 위한 수단으로 사용되며, 컴퓨터와 인터넷을 중심으로 한 정보화 사회가 도래함에 따라 그 중요성이 점점 증대되고 있는 핵심기술이다[2,3].

비밀 키 암호방식은 암호화와 복호화에 하나의 비밀 키를 사용한다. 송수신자 양측이 동일한 비밀 키를 가지고 통신을 하므로 대칭키 암호(Symmetric-Key Encipherment)방식이라고도 불리며, 안정성은 공개키 방식에 비해 다소 떨어지지만 구현 방식이 간단하고 동작이 빠르다. 블록 암호는 비밀 키 방식의 하나이며 암호문을 만들기 위해 암호 키와 알고리듬이 데이터 블록단위로 적용되는 특징이 있다.

미국 NIST(National Institute of Standards and Technology)가 AES(Advanced Encryption Standard) [4]를 블록암호 표준으로 채택한 이래로 강력한 보안성능과 다양한 운영모드의 장점으로 인해 무선 랜, Zigbee 등 다양한 유·무선 통신 시스템의 보안 알고리듬으로 폭 넓게 사용되고 있다.

최근, IoT 기술이 상용화되기 시작함에 따라 정보유통의 물리적인 안전성이 중요 이슈로 부각되고 있으며, 전용 하드웨어를 이용한 보안 시스템의 구현에 관한 연구가 활발히 이루어지고 있다. 대용량 데이터의 고속암·복호에 초점을 맞춘 하드웨어 구현을 비롯해서 스마트카드, NFC, IoT와 같은 휴대장치에 적합한 소면적, 저전력 하드웨어 구현 결과들이 발표되고 있다[5-9]. 고속 처리에 초점을 맞춘 하드웨어 구조는 높은 처리율을 갖는 장점이 있지만, 회로 복잡도나 전력소모 측면에서 휴대용 기기에 적합하지 않다.

본 논문에서는 국가보안기술연구소(NSRI)에서 개발한 128비트 블록암호 알고리듬 LEA[10]를 IoT 환경에 적합하도록 최적화한 LEA 암·복호 코어를 설계하였으며, FPGA 구현과 UART 통신, MFC를 이용한 데모프로그램을 통해 하드웨어 동작을 검증하였다.

본 논문은 다음과 같이 구성된다. Ⅱ장에서는 블록암호 알고리듬 LEA에 대해 간략히 설명하고, Ⅲ장에서는 LEA-128 암호·복호 프로세서 설계에 대해 설명한다. 설계된 회로의 기능 검증 및 FPGA 구현에 대해 Ⅳ장에서 기술하며, Ⅴ장에서 결론을 맺는다.

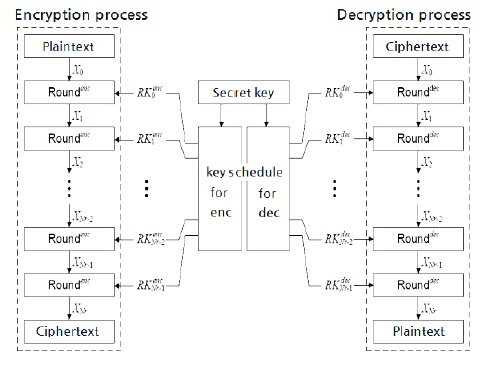

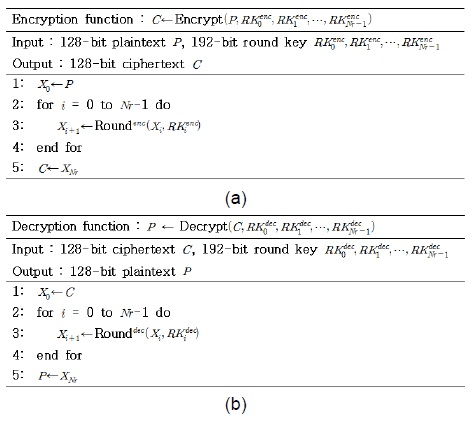

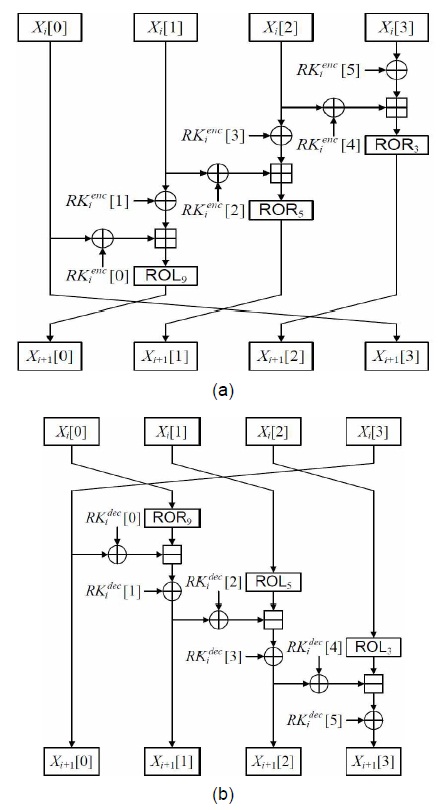

블록암호 LEA는 128비트의 평문(암호문) 블록을 128/192/256비트의 마스터키로 암호화(복호화)하여 128비트의 암호문(평문)을 생성하는 대칭키 방식의 암호 알고리듬이다. LEA는 ARX(Addition, Rotation, XOR) 연산을 기반으로 한 Feistel 유사 구조이며, 마스터키의 길이에 따라 24/28/32 라운드의 연산을 통해 암호화(복호화)가 이루어진다[2]. 128비트의 마스터키로 부터 생성되는 192비트의 라운드 키가 라운드 변환에 사용된다. 라운드 함수는 32비트 단위의 ARX 연산으로 구성되어, 이들 연산을 지원하는 범용 32비트 소프트웨어 플랫폼에서 고속으로 동작한다. 또한 라운드 함수 내부의 ARX 연산 배치는 충분한 안전성을 보장함과 동시에 S-box의 사용을 배제하여 경량 구현이 가능하도록 한다[3]. LEA의 암호화·복호화 과정은 그림 1과 같으며, 라운드 키를 생성하는 키 스케줄러와 암호화·복호화를 수행하는 라운드 함수로 구성된다. 암호화 와복호화 과정은 서로 역순으로 이루어지며, 복호화는 암호화 과정의 역연산 과정이다. 따라서, 암호화 과정에서의 모듈로 가산은 복호화 과정에서 모듈로 감산으로 구현되고, 순환이동도 반대방향으로 이루어진다.

암호화 과정은 비밀키

암호화 과정의

복호화 과정의

LEA의 키 스케줄링은 AR(Addition-Rotation) 연산과 32비트 modulo 연산에 사용되는 상수를 생성하는 상수생성부로 구성된다. 입력되는 비밀키의 길이에 따라 상수 생성부에서 생성되는 상수의 개수가 달라지며, 암호화 과정인지 복호화 과정인지에 따라 AR 연산의 순서가 반대로 적용된다. 암호화 키 스케줄링은 비밀키

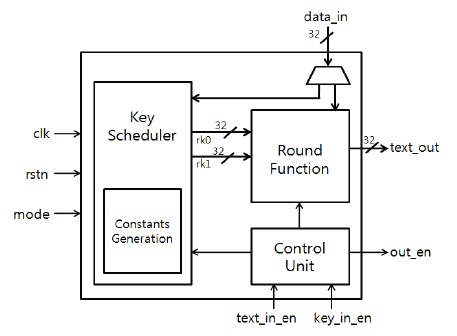

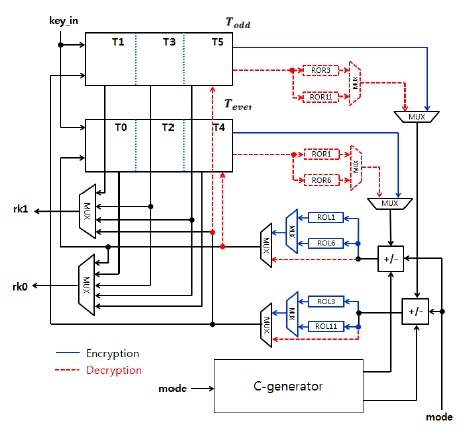

본 논문에서는 128비트의 평문(암호문) 블록을 128비트의 마스터키로 암호화(복호화)하여 128비트의 암호문(평문)을 생성하는 LEA-128 암호·복호 프로세서를 설계하였다. 설계된 LEA-128 코어의 전체 구조는 그림 4와 같으며, 라운드 블록, 키 스케줄링 블록, 제어 블록으로 구성된다. 라운드 블록은 24번의 라운드 변환을 통해 암호·복호 연산을 수행하며, 각 라운드의 연산은 3클록 주기로 처리된다. 키 스케줄링 블록은 각 라운드 연산에 사용되는 192비트의 라운드 키를 on-the-fly 방식으로 생성한다. 저면적 구현을 위해 라운드 블록을 32비트 회로로 설계하였으며, 입력 핀 (data_in)을 공유하여 마스터키와 평문(암호문)이 시분할 방식으로 입력되도록 하였다. 또한, 암호화와 복호화에서 하드웨어 자원이 공유되도록 설계하였다.

라운드 블록은 128비트의 평문(암호문) 입력과 키 스케줄러에 의해 생성되는 192비트의 라운드 키를 받아 라운드 연산을 반복적으로 처리하여 암호(복호)연산을 수행한다. 라운드 블록은 그림 5와 같이 구현되었으며, 4개의 32비트 내부 레지스터(

Text_in 포트를 통해 입력되는 128비트의 평문/암호문은 32비트 단위로 4클록 주기에 걸쳐 상태변수 레지스터

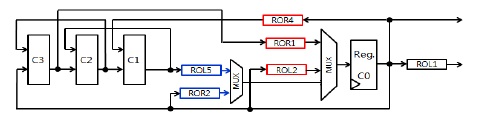

LEA의 암호화·복호화의 라운드 연산에 사용되는 192비트의 라운드 키는 키 스케줄링 알고리듬에 의해 생성된다. 설계된 키 스케줄링 블록은 그림 6과 같으며, 6개의 32비트 내부 레지스터(

128비트의 마스터키

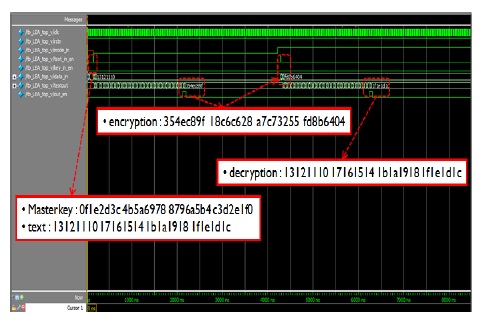

Verilog HDL로 설계된 LEA-128 코어의 기능검증 결과는 그림 8과 같으며, 128비트의 평문 “10111213 14151617 18191a1b 1c1d1e1f”와 128비트의 마스터키 “0f1e2d3c 4b5a6978 8796a5b4 c3d2e1f0”를 입력벡터로 사용한 시뮬레이션 결과를 보이고 있다. 암호화의 결과로 128비트 암호문 “9fc84e35 28c6c618 5532c7a7 04648bfd”이 출력되었고, 이를 다시 복호한 결과는 암호에서 입력으로 사용된 평문 “10111213 14151617 18191a1b 1c1d1e1f”이 출력됨을 확인함으로써 설계된 LEA-128 프로세서의 논리기능이 정상적으로 동작함을 확인하였다.

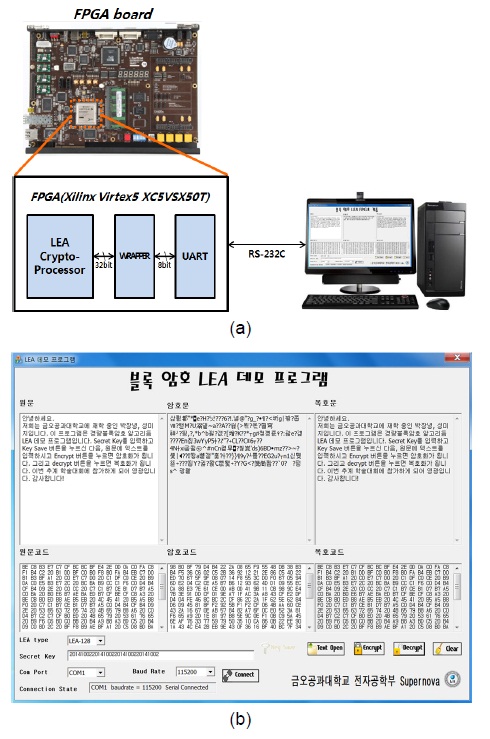

기능검증이 완료된 LEA-128 코어는 FPGA 구현을 통해 하드웨어 동작을 검증하였다. 그림 9(a)는 FPGA 보드, UART 인터페이스, 구동 소프트웨어로 구성된 검증시스템 구성되며, Xilinx Virtex5 XC5VSX-50T 디바이스가 사용되었다. PC에서 입력된 비밀키와 평문(암호문) 데이터가 RS232C 통신을 통해 FPGA에 인가되고, FPGA에서 출력되는 암호문(평문) 데이터가 화면에 표시된다. 그림 9(b)는 FPGA 검증 결과를 보이고 있다. 평문을 암호화하고, 암호문을 복호화하여 원래의 평문과 일치하는 복호결과가 출력되어 FPGA에 구현된 LEA-128 프로세서가 올바로 동작함을 확인할 수 있다. 설계된 LEA-128 프로세서는 암호/복호과정이 연속적으로 수행되도록 고려되었으며, FPGA 합성 결과 레지스터 600슬라이스, LUT 1418슬라이스, 총1498슬라이스로 구현되었고, 135.15MHz로 동작하여 216.24Mbps의 성능을 갖는 것으로 평가 되었다.

본 논문에서는 한국정보통신기술협회(TTA) 표준으로 등록된 128비트 블록암호 알고리듬 LEA-128을 하드웨어로 구현하여 동작을 확인하였다. 저면적과 저전력 구현을 위해 암호화와 복호화 과정에서 하드웨어 자원이 공유되도록 설계하였다. 설계된 LEA-128 암호·복호 프로세서는 IoT 및 모바일 기기 보안 등과 같이 저전력, 경량화가 요구되는 응용분야의 정보보호 코어로 활용이 가능할 것으로 예상된다.