In this paper, the conventional vertical structure for VLSI circuits CMOS intend to improve the stress effects of active region and built-in threshold voltage. For these improvement, the proposed structure is shallow trench isolation of moat shape. We want to analysis the electron concentration distribution, gate bias vs energy band, thermal stress and dielectric enhanced field of thermal damage between vertical structure and proposed moat shape. Physically based models are the ambient and stress bias conditions of TCAD tool. As an analysis results, shallow trench structure were intended to be electric functions of passive as device dimensions shrink, the electrical characteristics influence of proposed STI structures on the transistor applications become stronger the potential difference electric field and saturation threshold voltage, are decreased the stress effects of active region. The fabricated device of based on analysis results data were the almost same characteristics of simulation results data.

정보통신기술 (ICT : Information Communi cation Technology) 산업의 높은 경쟁력을 유지하기 위한 노력이 진행되고 있는 가운데 반도체소자의 미세화는 가장 중요한 핵심기술로 등장하고 있다. ICT 융합 사회가 필요로 하는 스마트 전자의 기술에서 고속, 고내압, 고집적화의 기본적인 소자제작을 위한 관련 기술이 절실하다. ICT산업의 급격한 변화에 대응하기 위해 반도체소자는 더욱 초고속, 고용량, 저전력 및 고신뢰성 제품개발이 요구되고 있는 실정이다. 이러한 요구 조건을 만족하기 위하여 반도체소자는 더욱 미세화 되어야하지만 고집적도의 미세화에서는 격리 형태의 물리적 한계가 있다. 기존의 CMOS를 이용한 집적회로는 고용량 IC제작에 한계를 보이고 있어 새로운 소자개발에 주력을 하고 있으며, 추후 3차원적인배열에 의한 집적도 향상에 노력하고 있다[1, 2].

소자의 미세화에 요구로 분석 툴은 격자 관련 온도와 전계에 대해 파라미터 유동에 관련이 있는 직접적인 열화를 예측할 수 없고, 툴 모델 파라미터는 균일 격자 가열 모델이며, 실재 적용할 때 차이가 있을 수 있다. 즉 절연막의 두께를 줄여야하는 초고집적화 소자 제작으로 소스와 드레인의 얕은 접합 형성을 위해서 소자와 소자 사이의 얕은 트랜치 격리는 트랜지스터 사이에서 전기적으로도 격리를 하기 때문에 CMOS 기술에서 중요한 공정 요소이다. 따라서 초고집적을 위한 소자와 소자를 격리 시키는 격리 공정 발달이 초고집적도에 중요한 관건이 되었으며, 이를 위한 최종적으로 성능과 생산량을 좌우하는 기본적인 물리적 현상에 대한 통찰력과 전기적 분석 결과가 제공하는 단위공정에 앞서 공정의 가능성과 소자의 특성을 미리 예측할 수가 있다[3, 4].

본 연구는 분석 툴(TCAD)을 이용하여 얕은 트랜치 격리 구조에 상호작용을 하는 두 가지 중요한 관련 인자와 특성 대한 특성과 이를 바탕으로 제안 구조의 소자 제작을 하고자 한다.

첫째는 얕은 트랜치 격리의 영향으로 소위 ‘좁은 폭 효과’라 불리는 좁은 폭의 MOS(Metal Oxide Semiconductor) 구조에서 기존에 주로 사용하는 수직모양 구조와 본 연구에서 제안하는 회자(Moat) 곡선화 구조에 따른 각각의 얕은 트랜치 격리 구조를 실제 공정을 고려한 구조별 전자농도 분포와 게이트 바이어스 대 에너지 밴드의 형태를 분석하고자 한다.

둘째는 이 구조에 따른 얕은 접합 격리에 의해 유기된 스트레스 때문에 얕은 트랜치 격리 공정이 활성 영역에 미치는 스트레스에 의한 실리콘의 손상이 근처의 트랜지스터 전기적 특성에 미치는 영향의 분석으로 전위 분포, 전계분포와 포화임계전압 특성을 분석하고자 한다.

셋째는 분석결과를 바탕으로 소자를 제작하여, 시뮬레이션 결과와 비교 분석을 하고자 한다.

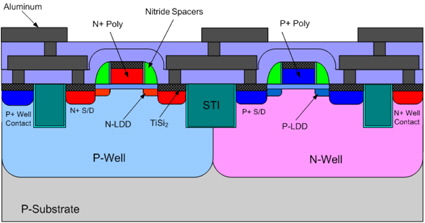

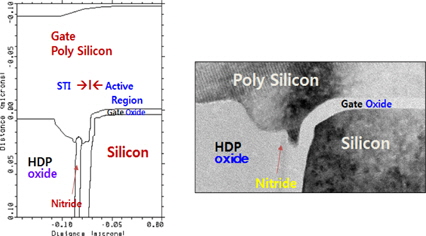

그림 1은 제안한 격리 구조를 이용하여 제작할 고집적 CMOS의 단면도이다.

분석용 툴은 2-차원 시뮬레이터를 이용하여, 제안한 얕은 트랜치 격리 구조와 기존의 격리 구조와의 사이에 동일한 조건에서 초고집적을 위한 얕은 접합의 소자가 요구하는 전계분포와 높은 임계전압이 나타나는 구조가 되도록 설계를 하여야 실제 제작에서 격리에 대한 활성영역의 영향이 작기 때문이다. 보고된[5, 6] 된 전형적인 45nm 기술 세대의 고성능 트랜지스터의 성능 CMOS 용도로 설계하고자 하는 전 단계 격리 공정 기술이다.

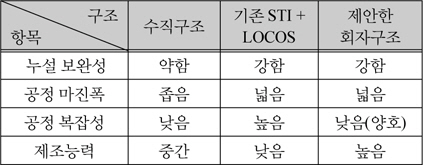

기존의 격리 구조에서 얕은 트랜치 격리와 활성영역 경계부위에 포화 임계전압을 개선시키기 위해기존의 1) 수직 모양 구조 2) 제안된 회자 모양의 구조에 따른 각각의 얕은 트랜치 격리 구조에서 동일한 분석 조건으로 전위에 대한 전자 분포, 전계분포를 분석한다.

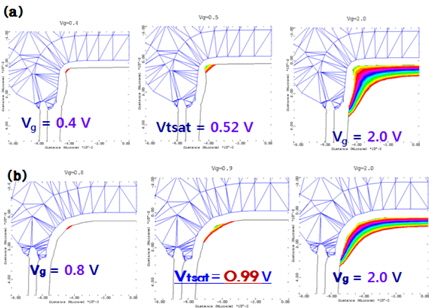

소자는 기판 P형으로 동일한 실리콘 기판농도1016 [/cm3]에서 실리콘과 실리사이드 전극인 게이트 단자에 0 [V]에서 2 [V] 까지 0.1 [V] 씩 증가 시키면서, 게이트 인가 바이어스의 크기에 따라서 트랜치 격리 구조의 가장자리에서 먼저 동일한 게이트 전압에 비해 얕은 산화막 두께로 인해 큰 전계가 형성되어 포화 임계전압에 도달하는 분석한 결과가 그림 2이다.

주요 전계 분포로 대표적인 전압 0.4 [V], 0.5 [V]와 2.0 [V]의 결과이다. a) 수직 구조이고, b)는 개선 시키고자하는 회자 모양에 대한 분석 결과이다. 게이트 단자에 바이어스를 인가한 결과 전자의 반전층이 0.8 [V] 이하에선 거의 전자농도 분포가 나타나지 않지만, 전압이 0.9 [V]에서 약간의 전자농도 분포를 나타내며, 1 [V] 근처와 유사한 포화 임계전압이 0.99 [V]로 나타난 확실하게 개선된 포화 임계전압 특성의 결과가 나타났다.

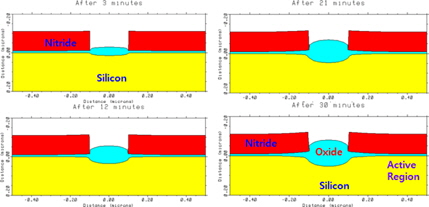

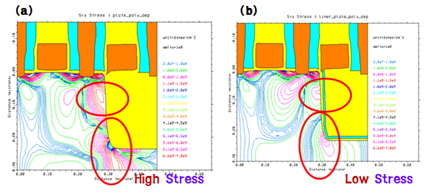

활성영역과 격리 산화막의 경계 부분의 가장자리의 분석으로 그림 3이다. 기존 수직 구조와 회자 구조에서 각 구조에 대해서 얕은 트랜치 격리 구조에서 산화막 형성 시 산화막의 두께 변화와 활성영역에 미치는 스트레스 영향을 분석한 결과이다.

분석 조건의 공정에서 초기 산화막은 열산화막 80 [Å]을 건식으로 형성시키고, 그 위에 실리콘 질화막을 화학기상증착 방법으로 1,000 [Å]을 증착을 시킨 다음 반응성이온 식각 장비를 이용하여 패턴 형성의 식각공정을 한 후 마스킹 물질을 포토레지스터로 나머지 영역의 실리콘 질화막, 산화막 형태로 구조를 만드는 과정이다. 격리를 위한 산화막 형성 조건에서 시간은 3분 간격으로 증가 시키면서 최종 30분 까지 단계 별로 증가 시킨 결과 분석 중에 특성의 차이가 확연히 나타나는 시간 조건으로 3분, 12분, 21분과 최종 30분에 대한 결과들이다.

그림 4는 게이트 전극 형성 시 게이트 활성영역의 가장자리에서 산화막의 두께가 미치는 영향을 분석하기 위한 효과적인 시뮬레이션 방법으로 매시 조견을 밀한 부분과 소한 부분으로 나타낸 그림(좌)와 게이트 가장자리의 산화막 두께가 실제 형성 과정을 구체적으로 나타난 결과이다. 산화 시 스트레스를 가장 많이 받는 부분의 영향으로 산화막 두께 결과가 다르게 나타난 결과이다. 분석으로 산화막의 형성 두께는 양 구조가 일정한 두께로 나타나며, 주요한 차이점은 산화막의 두께에 따른 격리 산화막의 모양에서 큰 차이점으로 인하여 기존의 수직 구조가 제안한 회자 구조 보다 활성 영역 가장자리 부위에 산화막 두께가 많이 두꺼워서 활성 영역부분에 스트레스 영향이 크면서 활성영역 부분도 일정 부분 잠식한 형태이다.

트랜지스터가 형성될 부분에 스트레스의 영향도 크게 나타났으며, 가장자리 부위의 스트레스의 영향으로 전기적 특성 분석에서 누설전류의 영향도 클 것으로 판단되며, 실제 트랜지스터 설계 시에 레이아웃 단계에서 이 영역을 고려해야 할 정도의 영향으로 나타난 결과로 분석되었다.

임계 전압이 개선된 결과에 대한 제안한 회자 구조의 얕은 접합 격리 구조를 제작하기 위한 공정 시뮬레이션은 TCAD 2-D 시뮬레이터를 이용하여, 제안한 얕은 트랜치 격리 구조의 시뮬레이션 연구는 최신 45nm 기술 세대의 고성능 트랜지스터의 성능 C-MOSFET 용도로 설계하고자 하는 전단계 공정 시뮬레이션 구조의 기술이다.

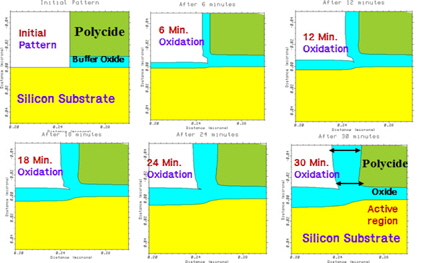

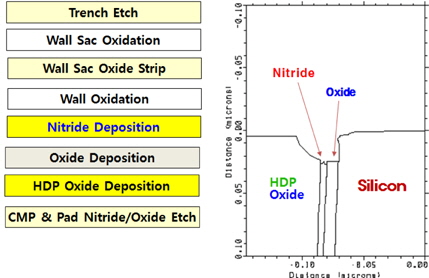

그림 5는 P-형 실리콘 기판에서 활성영역의 실리콘과 실리콘 질화막(Si3N4) 사이에 완충역할의 열산화막 80 [Å]을 건식으로 형성시키고, 화학기상증착(CVD) 방법으로 그 위에 실리콘 질화막을 1,000 [Å]을 증착을 시켜서 반응성이온 식각 장비를 이용하여 패턴 형성의 식각공정을 한 후 마스킹 물질을 포토레지스터로 나머지 영역의 실리콘 질화막, 산화막, 기판 실리콘을 2,000 [Å]을 트랜치 식각을 하는 구조로 여기에서 회자 모양으로 에칭을 한다.

몇 단계 후의 연속 공정 단계로 측면 벽을 완충역할의 열산화막을 다시 기른다. 이는 에칭 시에 스트레스가 많이 받은 부위는 산화의 속도가 빠르며, 이것이 제안한 회자 모양의 일부이다. 이를 다시 식각을 하여 제안된 구조를 제작코자 하였으며, 벽면에 다시 열산화막으로 80 [Å] 기른다. 그 옆에 화학기상증착(CVD) 방법으로 선형을 위한 실리콘 질화막 50 [Å]을 증착을 시키고, 그 위에 선형을 위한 화학기상증착(CVD) 방법으로 산화막 120 [Å]을 증착을 시킨다.

연속 공정으로 고밀도 플라즈마 산화막을 3,000 [Å] 증착시킨 후 화학 기계적 연마 (CMP) 장비로 고집적 전극의 원활한 형성을 위해서 웨이퍼 윗면부터 갈아낸 후 완충 산화막과 질화막을 식각 시킨 공정 단계이다.

트랜지스터 활성영역에서 소자의 임계전압 조절을 위한 이온 주입 시에 직접적인 실리콘의 손상 방지를 위한 차벽 산화막 형성을 한 후 이온 주입을 시키며, 이때 이온 주입 시에 손상된 차벽 산화막을 제거 한 후, 양질의 게이트 산화막을 형성 시키고, 게이트 전극용 다결정 실리콘 증착을 하여 전극을 형성한 전체 공정의 결과이다.

활성영역의 가장자리가 높은 임계 전압 특성을 나타나야 하는데, 이는 실제 임계 전압이 낮으면, 고집적 MOSFET 소자에서 가장자리 영역에서 채널이 형성되어 원하지 않는 누설 전류-전압 특성과 신뢰성의 문제점을 야기 시킬 수 있다. 따라서 얕은 트랜치 격리 구조에서 활성 영역의 가장자리의 높은 임계전압을 갖도록 격리 구조를 개선하는 일환으로 개선된 분석 결과이다.

그림 6은 부분에서 산화막 형성 시 활성영역에 미치는 스트레스 영향을 분석한 결과이다. 모서리 부분에서 스트레스의 영향이 크고, 벽면 부분에서 수직 구조가 스트레스가 미치는 플럭스 선이 조밀한 결과가 영향이 큰 것이며, 결과에서 회자 구조보다 훨씬 높은 스트레스의 영향으로 나타난 결과이다. 활성영역의 가장자리가 높은 임계 전압 특성을 나타나야 하는데, 이는 실제 임계 전압이 낮으면, 고집적 MOSFET 소자에서 가장자리 영역에서 채널이 형성되어 원하지 않는 누설 전류-전압 특성과 신뢰성의 문제점을 야기 시킬 수 있다.

따라서 얕은 트랜치 격리 구조에서 활성 영역의 가장자리의 높은 임계전압을 갖도록 격리 구조를 개선하는 연구를 지속적으로 하고 있다[3, 5].

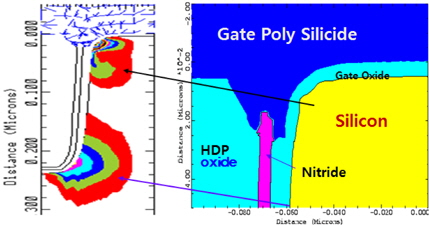

그림 7은 실리콘 기판에서 부터 공정 동안 얕은 트랜치 격리의 공정 단계에서 활성 영역의 실리콘 기판의 부위별 스트레스의 여부를 분석한 결과이다. 트랜치 식각 U자 모양의 깊이 0.2 [μm] 아래 부분 모서리에서 가장 스트레스로 인한 실리콘의 손상을 가장 많이 받았지만 이는 집적회로에서 소자의 제작 부분의 활성영역에서 소스/드레인의 일반적인 확산 깊이 0.1 [μm] 보다 훨씬 이하로 얕기 때문에 깊은 부위의 실리콘 손상으로 소자에 미치는 문제점은 거의 없는 것으로 판단된다.

전기적 특성의 영향 이외에 고집적회로의 제작 동안 실리콘-산화막 경계면은 도판트 불순물의 재분포에 영향을 미치는 것으로 잘 알려져 있다. 더욱이, 얕은 트랜치 격리로 사용할 때, 넓은 산화막 영역의 부피가 인접한 실리콘 활성화 영역에 스트레스를 인가한다. 소자의 크기가 축소됨에 따라서, 실리콘과 산화막 사이에 역학적 상호작용과 공정은 트랜지스터의 전기적 특성에 미치는 인자가 크고 피할 수 없는 영향을 준다.

그림 8은 시뮬레이션 분석 결과로 나타난 여러 단계를 실제 실리콘 공정에 응용하여 공정 분석 단계와 동일한 조건의 단계를 거쳐서 실제 회자모양의 제작한 얕은 트랜치 격리 공정의 결과 사진이다.

좌측의 시뮬레이션 결과와 우측의 제작한 소자의 단면도의 결과와 거의 대동소이한 모양을 나타내고 있다. 게이트 산화막 부분과 실리콘과 게이트 단자인 폴리 실리콘 부분은 명확하며, 고밀도 플라즈마 산화막과 질화막의 경계는 일부 흐릿하지만 다른 상위 부분은 선명한 경계 결과를 보인다.

고집적응 위한 여러 전기적 특성의 개선시킬 의도로 제안한 회자구조의 얕은 트랜치 격리를 여러 파라미터를 구조별로 분석하였으며 이를 바탕으로 소자를 제작하여 비교하였다.

분석 툴(ATHENA, ATLAS)을 이용한 시뮬레이션의 중요한 두 가지 결과인 좁은 폭 효과와 스트레스 관련 효과들의 특성을 제시하였다. 좁은 폭 효과에서 회자 모양의 STI는 포화 임계전압, 가장자리 스트레스에서 상당한 개선의 결과가 나타났으며, 제안한 회자 모양의 STI는 제작 공정에서의 실리콘의 공정 스트레스에 의한 손상 부위가 트랜치 격리의 밑 부분에 크며, 초고집적회로의 소자에 미치는 영향은 작은 것으로 판단된다.

또한 같은 채널 농도를 갖는 트랜지스터이라도 얕은 트랜치 격리의 구조에 따라서 포화 임계전압은 달라지며, 수직 구조 보다 제안한 회자 모양의 얕은 트랜치 격리 구조가 가장자리 영역에서 양호한 높은 포화 임계전압 특성을 보였다. 즉 구조에서 곡선화가 잘 된 것일수록 활성영역에서 평판과 가장자리의 전기적 특성이 비슷한 특성을 보인 결과였다.