In this paper, a phase locked loop with suppressed power supply noise has been proposed. The added negative feedback loop of voltage controlled oscillator(VCO) and power noise detector suppresses the power noise induced jitter variation of VCO down to 1/3. The power noise detector is the modified circuit of frequency voltage converter. The proposed PLL has been designed based on a 1.8V 0.18um CMOS process and proved by HSPICE simulation.

위상고정루프는 VLSI 설계에 중요한 역할을 한다. 고속의 클록 신호에 의해 동작하는 디지털 칩에서 위상고정루프는 주기가 일정한 클록 신호를 생성하는 회로로 사용된다. 이 지터의 크기가 출력 신호의 정확도와 다른 주기를 가진 신호의 크기를 결정하기 때문에 흔들리지 않는 정확한 주기를 갖는 클록 신호 (clock timing jitter)의 지터 크기는 중요하다. 오늘날의 미세 CMOS 공정에서는 전원전압의 크기는 전력소모를 줄이고 소자 및 회로의 신뢰성을 증가시키기 위하여 작아지고 있다. 이런 낮은 전원전압에서는 디지털 회로의 스위칭에 위한 잡음이 전압제어발진기(VCO)의 출력 신호에 다른 주파수 성분의 크기를 증가시켜 출력 신호의 정확도를 떨어트린다. 인버터 또는 차동 형태의 인버터를 사용한 링구조 VCO에서 조그마한 전원전압 변화는 지터 크기에 큰 영향을 준다[1, 2]. 전원전압 잡음은 링구조 VCO를 사용하는 위상고정루프가 디지털 칩에서 클록 신호 생성기로 사용되는데 가장 큰 걸림돌이 된다[3]. 그러므로 링구조 VCO를 사용하는 위상고정루프가 디지털 칩에 집적화되기 위해서는 전압전압 변화에 둔감하게 반응하게 설계하여야 한다.

전원전압 잡음을 억제하기 위해 다양한 구조의 전원 전압제어 기법이 사용되었다[4-6]. 이러한 구조에서는 전원전압은 연산증폭기와 구동 트랜지스터와 구성된 low-dropout 선형조절기로 통해 VCO로 전달된다. 그러 므로 VCO 전원전압은 구동 트랜지스터의 VDS에 의해 VDD 보다 작은 값을 가지므로 VCO 동작 전압 범위가 좁아진다. 또한, low-dropout 선형조절기에 발생하는 극점으로 인하여 이 궤환 회로를 안정하게 위하여 보상 회로가 필요하다. 논문 [7]에서는 잡음을 억제하기 위해 서는 전력 소모가 많은 것을 피하기 위하여 조절기를 위상고정루프에서 분리하여 설계하였다. 이 구조에서는 조절기 궤환 회로와 위상고정루프 대역폭을 적절히하여 전체 위상고정루프 잡음 특성을 좋게 하기 위해서는 큰 크기의 디커플링 커패시터가 필요하다. 디지털 위상고정루프에 사용하기 위해 PVT 변화에 둔감한 공급전압 잡음억제 조절기를 설계하였다[8]. SOI 공정을 이용하여 위상고정루프의 전원잡음의 크기를 줄인 구조도 발표되었다[9]. 이 구조는 SOI 공정의 deep trench 커패시터가 요구된다.

이 논문에서는 전원전압 잡음 감지 회로를 링구조 VCO에 연결하여 전원전압 잡음에 의한 지터 변화를 크게 줄였다. VCO의 전원전압 잡음을 억제하는 부궤환루프와 전체 위상고정루프 부궤환 루프로 구성되어 있다. 제안한 위상고정루프는 0.18μm CMOS 공정을 사용하여 HSPICE 시뮬레이션을 통해 결과를 검증하고자 한다.

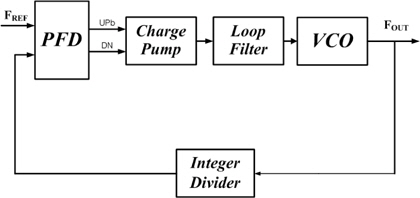

가장 기본적인 위상 고정 루프는 그림 1과 같이 위상 주파수 검출기, 전하 펌프, 루프 필터, 전압 제어 발진기, 주파수분주기로 이루어진다. 먼저 위상 주파수 검출기에서 전압제어 발진기 출력을 일정 분주비로 분주한 주파수분주기의 출력 주파수와 기준 주파수를 비교하여 위상 차이만큼 전압 펄스 형태로 신호를 출력한다. 전하 펌프에서는 펄스 폭 시간 동안 전류를 다음 단인 루프 필터에 공급한다. 루프 필터에서는 전류를 전압의 형태로 바꾸어 전압 제어 발진기의 전압 제어 입력으로 인가되고, 전압 제어 발진기는 그에 해당하는 주파수를 최종 출력 한다. 하지만 전원에 잡음이 발생하게 되면 VLPF의 전압에 영향을 미치기 때문에 전압 제어 발진기의 출력 주파수에 지터가 더 발생하게 되고, 기본적인 구조의 위상 고정 루프에서는 이것을 보상하여 더 안정적인 주파수를 출력하는 것이 쉽지 않다.

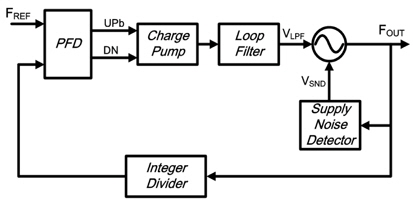

본 논문에서 제안한 위상 고정 루프 회로는 전원에 잡음이 발생했을 경우, 잡음에 보상하는 회로를 부궤환 회로로 구성하여 잡음에 대해 보상하는 전원 전압 잡음 감지 회로를(supply noise detector: SND) 부궤환 회로로 구성하여 잡음에 대해 보상하도록 동작하게 설계하였다. 그림 2에서는 제안한 위상 고정 루프의 전체 블록 다이어그램을 나타내고 있다. 동작을 살펴보면, 만약 공급 전압이 잡음에 의해 하강하게 되면 전압 제어 발진기의 출력 주파수와 전원 잡음 제거 회로 내부의 전류는 낮아지고, VSND 전압도 낮아진다. VSND 전압이 낮아지면 전압 제어 발진기에서는 VSND 전압이 낮아진 만큼 다시 주파수를 상승하게 한다. 반대로, 공급전압이 잡음에 의해 상승하게 된다면 전압 제어 발진기의 출력 주파수와 전원 잡음 제거 회로 내부 전류는 상승하게 되고 VSND 전압은 상승하게 된다. 그 후 전압 제어 발진기는 상승한 VSND 전압만큼 출력 주파수를 다시 낮추게 된다. 마지막으로, 공급 전압에 아무런 잡음이 인가되지 않고, 전압 제어 발진기의 내부 잡음에 의해 주파수가 상승 또는 하강한다면 위와 마찬가지 동작으로 주파수의 흔들림을 억제한다.

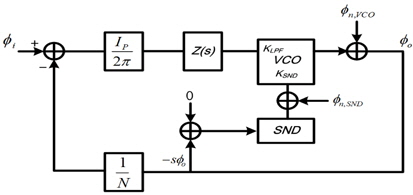

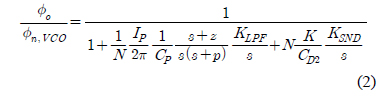

그림 3은 제안한 위상 고정 루프의 내부 잡음과 부궤환 경로를 고려한 선형 모델이다.

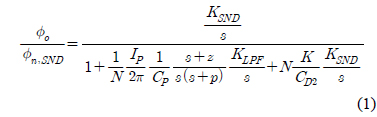

이 수식에서 Φn.SND와 Φn.VCO는 각각 전원 전압 잡음 감지 회로와 전원 전압의 잡음의 크기이다.

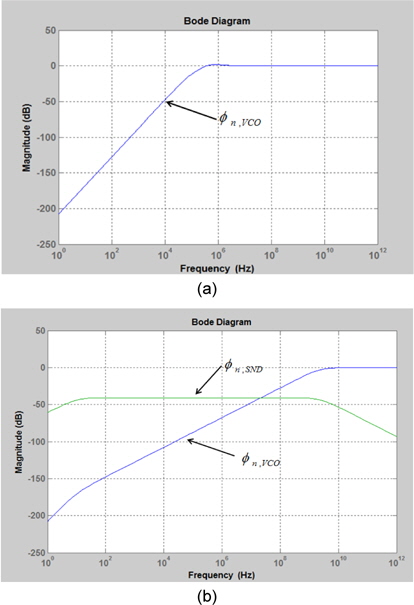

그림 4 (a)는 기존 구조에서 구한 전원 잡음 전달 함수이다. 그림 4 (b)는 식 (1)과 (2)를 이용하여 구한 전달 함수 이다. 그림 4 (b)는 그림 (a)와 비교하여 전원 잡음이 크게 감소하는 하는 것을 보여 주고 있다.

전원 전압 잡음 감지 회로의 잡음인 Φn.SND는 절대 값이 Φn.VCO에 비해 아주 작으므로 지터 특성에 영향을 거의 주지 않는다.

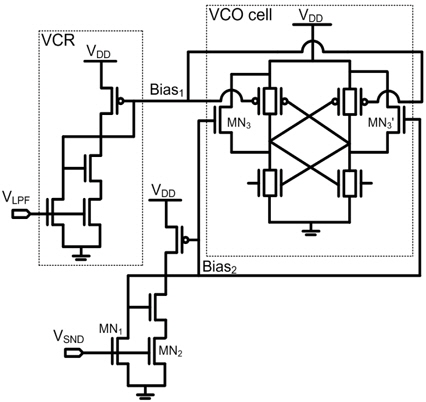

전압 제어 발진기는 두 개의 입력을 받아 한 개의 출력이 발생하도록 설계하였다. 그림 5에는 사용된 전압 제어 발진기의 회로를 나타내었다. VCR은 전압 제어 저항으로써 전압에 따라 선형적으로 전류를 VCO Cell에 전달하는 역할을 한다. MN3와 MN3'이 NMOS로 설계된 이유는 VSND전압이 감소하면 Bias2전압이 높아지게 되고, MN3와 MN3'에 전류를 더 많이 흐르게 하여 전압 제어 발진기의 출력 주파수를 더 높이기 위해서이다.

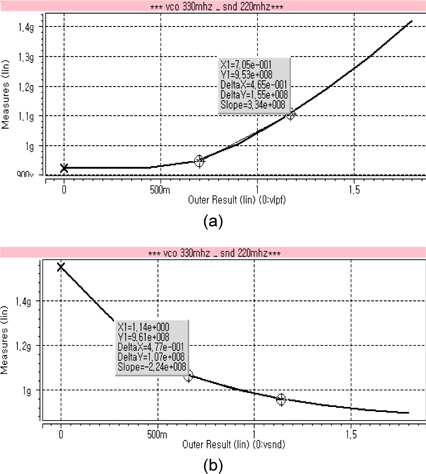

루프 필터의 출력인 VLPF와 전원 잡음 감지 회로의 출력인 VSND를 입력으로 받아서 동작을 하는데, VLPF 전압에 대해서는 전압이 상승할수록 주파수가 더 높아지도록 설계하고, VSND 전압에 대해서는 하강할수록 주파수가 더 높아지게 설계하였다. 그림 6은 사용된 전압 제어 발진기의 전압 대 주파수 특성을 나타낸 것이다. 시뮬레이션 결과를 보면 VLPF 전압이 점점 증가함에 따라 전압 제어 발진기의 주파수가 상승하고, 반대로 VSND 전압에 대해서는 감소함에 따라 주파수가 상승한다.

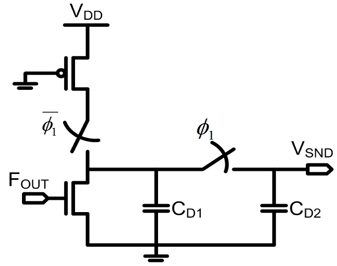

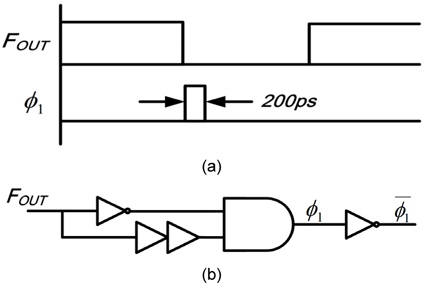

그림 7에는 전원 잡음 감지 회로의 내부 구조를 나타내었다. 2개의 MOSFET과 2개의 스위치, 2개의 커패시터로 구성되어 있는데, 각각의 스위치는

전원 잡음 감지 회로에 쓰인 CD1과 CD2 커패시터의 관계는 2CD1=CD2 이다. 그리고 VSND전압이 전압 제어 발진기의 입력부에 인가되면서 전달특성에 문제가 생기지 않게 하기 위해 CD2 커패시터의 최솟값을 VSND 노드가 전압 제어 발진기 쪽을 바라보았을 때 커패시터 값의 10배로 정했다. VSND 노드에서 바라본 MOSFET 크기와 HSPICE 라이브러리에 있는 산화막 두께로 계산한 결과 CD2의 최솟값은 65.32fF이 나왔다. 여기서는 CD2를 1pF으로 해서 전압이 튀는 현상을 최대한 완화했다.

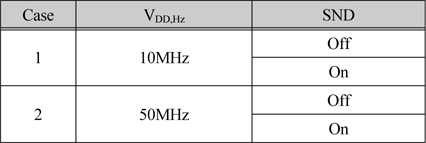

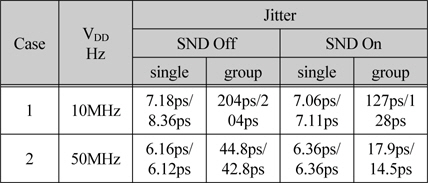

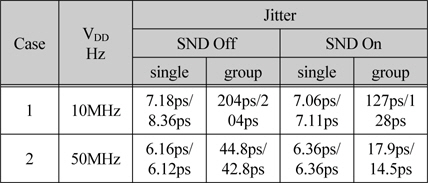

전원 잡음 감지 회로의 잡음에 대한 효과를 알아보기 위해 아래 표 1과 같이 공급 전압에 임의의 사인파를 잡음으로 인가하여 시뮬레이션을 수행하였다. 지터 감소를 좀 더 명확하게 알기 위해 전원 잡음 감지 회로가 있을 경우와 없을 경우로 나눠서 결과를 비교하였다. 추가로 그림 1과 같은 가장 기본적인 구조의 위상 고정 루프같은 경우에는 지터가 상승 시간에는 4.92ps, 하강 시간에는 5.05ps로 나타났다. 상승과 하강 신호가 다른 지터 값을 가지는 이유는 그림 4의 VCO 내부 NMOSFET와 PMOSFET의 “on/off” 시간이 달라 발생 하는 것으로 추정된다.

시뮬레이션 경우의 수

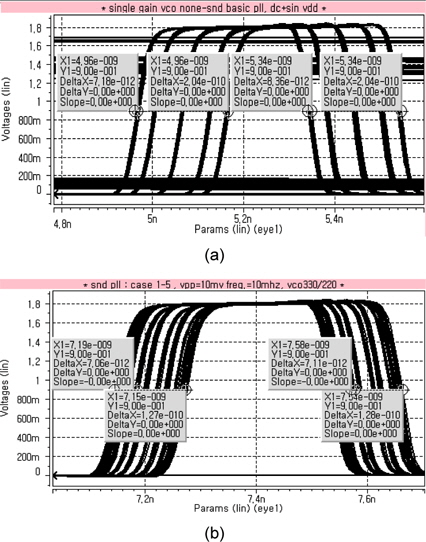

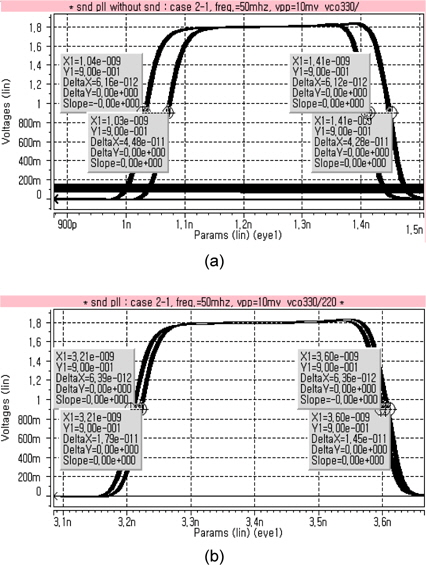

경우1의 전원 잡음 감지 회로 유무에 따른 지터 시뮬레이션 결과를 그림 9에 나타내었다. 먼저 전원에 인가된 사인파 형태의 잡음 때문에 지터의 모양이 일반적으로 나타나는 단일 형태가 아니고, 단일 형태의 지터가 여러 개로 나뉘어 그룹을 형성하고 있는 것을 알 수 있다. 그림 9(a)는 전원 잡음 감지 회로가 없는 경우를 나타낸 것인데, 단일 형태의 상승/하강 지터는 각각 7.10ps, 8.36ps로 나타나고, 그룹 형태의 상승/하강 지터는 204ps, 204ps로 나타난다.

그림 9(b)는 똑같은 조건에서 전원 잡음 감지 회로를 연결 했을 때를 나타낸 결과인데, 각각의 단일 형태의 상승/하강 지터가 7.06ps, 7.11ps로 나타나고, 그룹 형태의 상승/하강 지터는 127ps, 128ps로 전원 감지 회로가 없을 경우보다 더 작게 나타난 것을 알 수 있다.

마찬가지로 Case 2에는 앞선 경우보다 더 높은 주파수로 전원에 잡음을 인가하여 시뮬레이션 했는데, 그 결과는 그림 10과 같다. 이 경우, 단일 형태의 지터는 전원 잡음 감지 회로가 꺼져있을 경우보다 크게 나왔지만, 전체 그룹 형태의 지터를 측정한 결과 1/3배로 줄어든 것을 확인 할 수 있다.

표 2는 경우의 수에 따른 시뮬레이션 결과를 정리해 놓은 것이다.

시뮬레이션 결과표

본 논문에서 제안한 위상 고정 루프는 기본적인 구조에 전원 잡음 감지 회로를 부궤환으로 내부에 추가한 형태이다. 제안된 구조는 전력소모가 크고, 면적이 많이 요구되는 복잡한 기존구조와 다르게 간단하면서도 잡음제거 기능은 유사하다. 공급 전원에 잡음이 발생할 경우 전원 잡음 감지 회로는 잡음의 보상 형태로 출력을 발생시켜 전압 제어 발진기의 출력 주파수의 변동폭을 줄이도록 하였다. 잡음을 각각의 경우의 수로 시뮬레이션 한 결과 전압 제어 발진기의 지터 특성이 전원 잡음 감지 회로가 있을 경우 개선되는 것을 확인할 수 있다.