In this paper, the impact of substrate bias(VBS) on the zero capacitor RAM(Z-RAM) in n-channel junctionless multiple gate MOSFET(MuGFET) has been analyzed experimentally. Junctionless transistors with fin width of 50nm and 1 fin exhibits a memory window of 0.34V and a sensing margin of 1.8×104 at VDS=3.5V and VBS=0V. As the positive VBS is applied, the memory window and sensing margin were improved due to an increase of impact ionization. When VBS is increased from 0V to 10V, not only the memory window is increased from 0.34V to 0.96V but also sensing margin is increased slightly. The sensitivity of memory window with different VBS in junctionless transistor was larger than that of inversion-mode transistor. A retention time of junctionless transistor is better than that of inversion-mode transistor due to low Gate Induced Drain Leakage(GIDL) current. To evaluate the device reliability of Z-RAM, the shifts in the Set/Reset voltages and current were measured.

기존의 1개의 트랜지스터와 1개의 커패시터(1T/1C)로 이루어진 DRAM의 한 셀 당 크기가 나노미터로 감소하면서 여러 가지 문제점들이 발생하고 있다. 트랜지스터는 채널길이의 감소에 따라 발생하는 단채널 현상으로 인하여 누설전류가 증가하게 되며 커패시터는 면적 감소로 인하여 전하축적 용량이 감소하게 된다. 이는 DRAM 스케일링 시 보유시간(Rentention time) 및 내구성(Endurance) 등의 메모리 특성 저하의 주된 요인이 된다. 특히, 커패시터의 경우 메모리 동작을 위해선 각 셀 당 전하축적 용량이 적어도 30fF/cell 은 되어야하며[1], 이를 위해선 설계 시 stack 및 deep-trench 등 복잡한 공정이 필요하여 DRAM 셀의 추가적인 스케일링의 주된 장애 요인이 되고 있다[2]. Z-RAM 의 경우 커패시터가 없이 1개의 트랜지스터만으로 DRAM 셀을 구현한 구조로 복잡한 커패시터 설계를 제거하므로 스케일링 시 장점을 가지고 있어 많은 연구가 진행되고 있다[3-6]. Z-RAM 은 수평전계가 증가함에 따라 고에너지의 캐리어들이 충돌하면서 발생하는 충격이온화를 이용, 기판에 다수 캐리어를 축적시켜 부유 기판 효과(Floating body effect) 를 일으키는 방식[3], 게이트와 드레인의 오버랩 영역에서 밴드 간의 터널링으로 인하여 발생하는 게이트 유도 드레인 전류(Gate Induced Drain Leakage: GIDL) 현상을 이용하여 부유 기판 효과를 일으키는 방식[4], 기생 양극성 트랜지스터 (Parasitic bipolar transistor: PBT) 효과에 따른 소자의 순궤환 현상을 이용하는 방식[5], 결합 효과를 이용하여 채널의 다수 캐리어를 일시적으로 공핍시키면 전하의 불균형에 따른 비평형 상태가 되며 다수 캐리어가 생성되어 평형 상태에 도달하는데 걸리는 시간을 이용하는 동적결합 효과(Dynamic coupling effect) 방식[6] 등을 이용하여 0과 1을 구분한다. 기생 양극성 트랜지스터 효과를 이용하여 Z-RAM(이하 PBT-RAM) 을 구동 시키는 경우 기판이 완전하게 공핍되는 구조에서도 동작이 가능하므로 단채널 현상이 감소하여 스케일링 시 유리하며, 높은 센싱 마진(Sensing margin)과 뛰어난 보유시간 특성을 보여주고 있어, 활발한 연구가 이루어지고 있다. 하지만 PBT 효과를 유지하기 위해선 높은 구동전압이 필수적이므로 큰 전력소비 및 hot carrier effect(HCE)에 의한 소자열화의 문제가 존재한다[7].

반전모드(inversion mode: IM) 소자를 이용한 PBTRAM의 경우 양의 기판 전압 인가를 통해 순궤환 현상이 발생하기 위한 최소 구동전압을 낮출 수 있으며 센싱 마진을 개선시킬 수 있다 [8]. 하지만 이는 소스와 채널간의 전위장벽이 낮아져 기판에 축적된 홀들이 소스단자를 통하여 흘러나가는 결과를 초래, 보유시간 특성이 저하되며[9], 기판 전압이 일정 전압 이상 초과 시 오히려 메모리 윈도우(Memory window)가 감소한다[6]. 매몰 산화층 두께를 얇게 해서 만든 SOI 웨이퍼에 Z-RAM 을 제작하는 경우 메모리 셀의 기판에 펄스를 인가함으로 셋 전압을 낮추고 보유시간 특성도 개선시킬 수 있다는 논문이 발표되기도 하였다[10].

2010년 무접합(junctionless: JL) 소자를 Z-RAM 으로 사용하면 고농도로 도핑된 채널에서의 밴드 갭 감소현상과 고온도의 전자영역이 넓게 형성되어 더 낮은 구동 전압으로도 충격이온화가 발생, 저전압, 저전력 Z-RAM 의 구현이 가능하다고 발표되었다[11]. 하지만 무접합 소자의 경우 반전모드 소자의 비해 메모리 윈도우가 좁아서 셋/리셋 전압 설정 시 어려움이 따를 것으로 예상되며, 구동전류가 작은 단점이 있다. 반전모드소자는 기판에 전압을 인가하여 PBT-RAM 의 성능을 개선하는 연구들이 많이 진행되었으나, 무접합 소자의 기판 전압에 따른 PBT- RAM 특성 변화와 관련한 연구는 아직 전무하다.

본 연구에서는 기판 전압이 무접합 및 반전모드 소자의 PBT-RAM 특성에 미치는 영향을 비교, 분석하기 위하여 기판 전압에 따른 이력곡선(hysteresis loop) 측정을 실시하였으며, 반복적인 측정을 통한 셋/리셋 전압, 전류 변화를 통하여 무접합 PBT- RAM 의 신뢰도를 평가하였다.

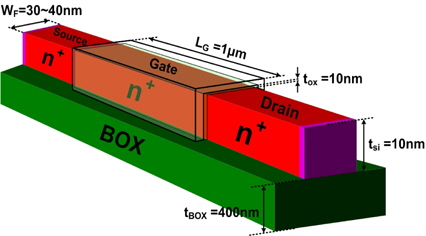

n-채널 다중게이트 무접합 및 반전모드 소자는 실리콘 박막의 두께가 340nm이며 저항이 10-20

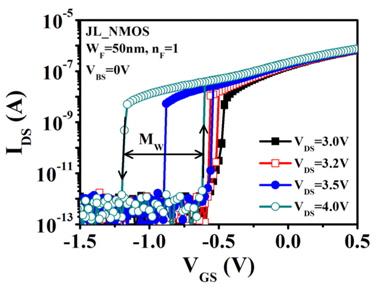

그림 2는 드레인 전압에 따른 n-채널 무접합 소자의 이력곡선(hysteresis loop) 그래프이다. 드레인 전압이 증가하면서 메모리 윈도우가 넓어지는 것을 확인할 수 있다. 드레인 전압이 높아짐에 따라 채널의 수평방향 전계가 커지게 되고 충격이온화가 많이 일어나면서 전자/홀 쌍의 수가 증가하게 된다. 충격이온화로 생성된 홀이 재결합 하는데 소요되는 시간이 증가, 순궤환 현상이 오래 지속되어 메모리 윈도우(MW)가 넓어진다.

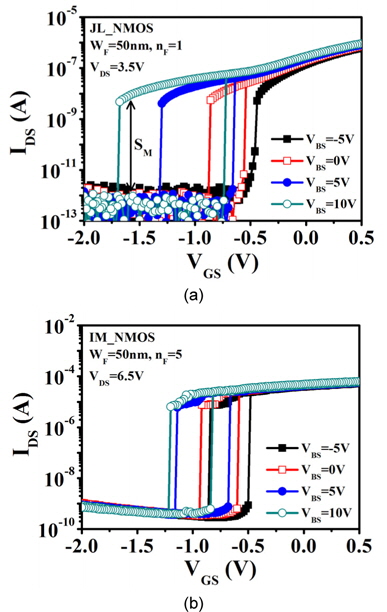

그림 3은 핀 폭이 50nm 로 동일한 n-채널 무접합 및 반전모드 소자의 기판 전압에 따른 이력곡선 특성을 나타낸 그림이다. 무접합 소자의 경우 VDS=3.5V에서 이력곡선 현상이 발생하는 반면 반전모드 소자의 경우 VDS=6.5V에서 발생하는 것을 확인할 수 있다. 실리콘 표면의 반전 채널에서 충격이온화가 발생하는 반전모드 소자와 달리 무접합 소자의 경우 전류전도 대역이 실리콘 박막 중심부(Bulk) 에 위치한다. 표면 충격이온화의 경우 Bulk 충격이온화 보다 약 40% 더 높은 드레인 전압에서 발생하므로, 반전모드 소자의 이력곡선 특성이 나타나기 위해선 무접합 소자에 비하여 더 높은 구동 전압이 요구된다 [13]. 무접합 소자의 경우 더 낮은 드레인 전압에서도 순궤환 현상이 발생하기 때문에 소비전력 및 HCE 에 의한 소자열화 측면에서 기존 반전모드 소자 보다 우수하다.

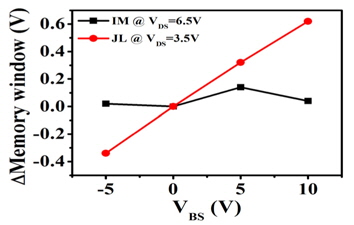

기판 전압에 따른 무접합 및 반전모드 소자의 메모리 윈도우 변화를 그림 4에 나타내었다. 무접합 소자의 경우 전류전도 대역이 실리콘 박막 중심부에 위치하기 때문에 상측 게이트와 채널간의 유효 게이트 커패시턴스가 감소하며[14], 상대적으로 기판 전압이 전류전도 대역에 미치는 영향이 더 크다. 기판 전압에 따른 무접합소자의 충격이온화 변화율이 반전모드 소자 보다 크기때문에, 무접합 소자의 메모리 윈도우 변화 값이 반전모드 소자보다 큰 것으로 사료된다. 또 한 가지 차이점은 VBS=10V일 때 무접합 소자의 메모리 윈도우는 증가한 반면 반전모드 소자는 소폭 감소한 것을 볼 수 있다. 반전모드 소자의 경우 하부 채널 문턱전압 보다 더 큰기판 전압이 인가되면 실리콘 박막 하부에 전류전도 대역이 형성, 축적되어 있던 홀들이 하부 채널을 통하여 소스 단자로 빠져나가면서 메모리 윈도우가 감소한다[8] 반면, 무접합 소자의 경우 전류전도 대역이 실리콘 박막 중심부에 위치하며 추가적인 채널 형성이 되지 않기 때문에, 기판에 큰 전압이 인가되어도 메모리 윈도우가 증가하는 것으로 보인다.

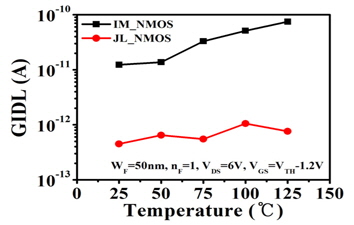

그림 5는 온도에 따른 무접합 및 반전모드 소자의 게이트 유도 드레인 전류(GIDL) 전류를 나타낸 그래프다. 무접합 소자의 GIDL 전류가 반전모드 소자에 비해서 작은 것을 볼 수 있으며, 온도가 상승함에 따라서 그 차이가 증가하는 것을 확인할 수 있다. 게이트와 소스/드레인 접합의 중복 영역에서 밴드 간의 터널링 현상으로 발생하는 GIDL 전류의 경우, 소스/드레인 추가 도핑에 따른 접합이 없는 무접합 소자가 접합이 존재하는 반전모드 소자에 비해서 더 낮은 것으로 알려져 있다[15]. PBT-RAM 의 경우, GIDL 전류가 증가함에 따라 보유시간 특성이 감소하는 것으로 알려져 있으며[16], GIDL 전류가 작은 무접합 소자의 보유시간 특성이 기존 반전모드 소자에 비해서 더 우수할 것으로 사료된다.

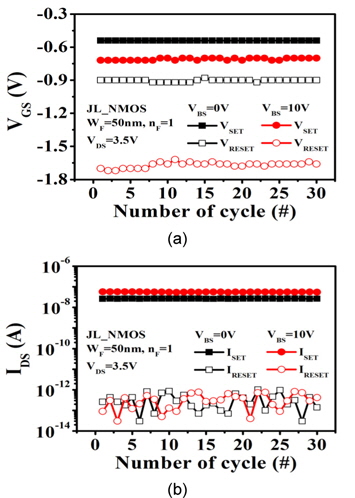

무접합 소자의 신뢰성을 평가하기 위해서 반복적인 측정을 실시하였으며 측정 횟수에 따른 셋/리셋 전압(VSET/VRESET) 및 전류(ISET/IRESET)의 변화를 그림 6에 나타내었다. 셋/리셋 전압은 렛치 업/다운 현상이 발생하는 지점의 게이트 전압으로 정의하였다. 기판 전압이 0V 인 경우 30번의 반복적인 측정에도 셋 전압은 변하지 않았으나 기판 전압이 10V 인 경우 약간의 변화를 확인할 수 있다. 리셋 전압의 경우 기판 전압이 0V 일때는 약간의 변화 있지만, 기판 전압이 10V 인 경우 조금씩 증가하는 것을 볼 수 있다. 전류는 VBS=0V, 10V 두 전압 조건 모두 셋 전류 및 리셋 전류의 변화가 없는 것을 확인 할 수 있다. 그림 6으로부터 무접합 소자의 신뢰성이 우수한 것을 볼 수 있으며, 이는 전류전도 채널이 실리콘 박막의 중심부에 위치하는 무접합 소자의 경우 게이트 산화층으로 주입되는 hot carrier 수가 감소하면서 계면상태가 적게 발생하기 때문이다.

기판 전압이 무접합 PBT-RAM 의 DC 메모리 특성에 미치는 영향을 분석하였다. 무접합 소자의 인가된 기판 전압이 0V 에서 10V 로 증가함에 따라서 메모리 윈도우는 0.34V 에서 0.96V, 센싱 마진은 1.8×104 에서 3.6×104로 증가하였다. 무접합 소자의 경우 반전모드 소자에 비해 더 낮은 드레인 전압에서도 PBT-RAM 으로 동작하였으며, 기판 전압에 따른 메모리 윈도우와 센싱 마진의 변화율은 무접합 소자가 반전모드 소자보다 더 크다. 기판 전압이 10V 인 경우 반전모드 소자의 메모리 윈도우 값은 감소하였으나 무접합 소자는 증가 하였다. 반전모드 소자의 GIDL 전류 크기가 무접합 소자의 경우보다 컸으며 이를 통해 무접합 소자의 보유시간 특성이 반전모드 소자에 비해서 더 우수할 것으로 사료된다. 전류전도 채널이 실리콘 박막 중심부에 위치하는 무접합 소자의 경우 PBT-RAM 동작 시에 신뢰성이 우수하다.