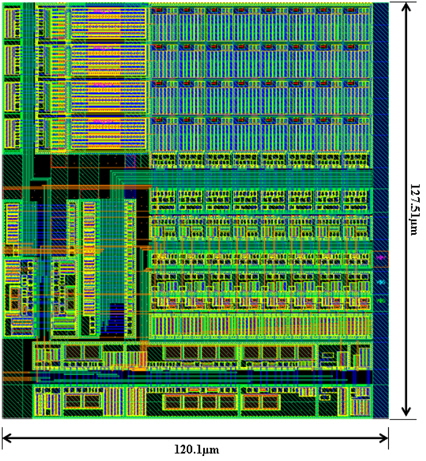

In this paper, a small-area cell array method of reducing number of SL drivers requiring large layout areas, where the SL drivers supplying programming currents are routed in the row direction in stead of the column direction for eFuse OTP memory IPs having less number of rows than that of columns such as a cell array of four rows by eight columns, and a core circuit are proposed. By adopting the proposed cell array and core circuit, the layout area of designed 32-bit eFuse OTP memory IP is reduced. Also, a V2V (=2V±10%) regulator necessary for RWL driver and BL pull-up load to prevent non-blown eFuse from being blown from the EM phenomenon by a big current is designed. The layout size of the designed 32-bit OTP memory IP having a cell array of four rows by eight columns is 13.4% smaller with 120.1㎛ × 127.51㎛ (=0.01531㎜2) than that of the conventional design with 187.065㎛ × 94.525㎛ (=0.01768㎜2).

x-ray 라인 스캔 센서는 x-ray를 통해 피사체 정보를 라인 스캔 센서를 이용하여 한 라인씩 검지하여 전기적 인 영상신호로 변환하는 장치이다. x-ray 라인 스캔 센서는 그림 1에서 보는바와 같이 픽셀 어레이, 행 디코더(row decoder), S/H 회로와 column select 회로, ASP(Analog Signal Processing) 회로와 timing generator로 구성되어 있다[1].

x-ray 라인 스캔 센서는 DC-DC 변환기에서 공급되는 VRESET(=2.7V)와 VCC(=4.3V)를 트리밍하거나, 그림 2의 ASP 회로에 사용되는 VGA(Voltage Gain Amplifier)의 gain 코드인 GAIN[2:0]를 지정해주기 위해서는 소용량의 비휘발성 메모리를 필요로 한다.

VGA 회로는 그림 2의 AMUX(Analog Multiplexer) 의 출력전압인 △V를 증폭하는 회로이다.

x-ray 라인 스캔 센서에 내장되는 비휘발성 메모리는 추가 공정이 필요 없는 로직 공정 기반 설계가 가능한 eFuse OTP (electrical Fuse One-Time Programmable) 메모리가 많이 사용되고 있다[2]. eFuse OTP 메모리는 eFuse에 수 십 mA의 과전류를 흘려 blowing하여 프로그램 한다[3,4]. eFuse의 프로그램 이전 저항은 50~100Ω 정도이고, eFuse 링크를 통해 프로그램 과전류가 흐르면서 eFuse의 프로그램 후 저항은 대개 수 십 ㏀ 이상이 된다. 이와 같이 eFuse는 한 비트의 디지털 데이터를 전도 상태와 고저항 상태 중 하나로 프로그램한다.

32비트 eFuse OTP 메모리가 필요한 경우 OTP 셀 어레이 사이즈는 1행 × 32열과 4행 × 8열로 배열할 수 있다. 2가지 형태의 eFuse OTP 셀 어레이 사이즈에 따른 OTP IP의 레이아웃 면적을 비교한 결과 4행 × 8열의 32비트 eFuse OTP의 면적이 1행 × 32열의 32비트 eFuse OTP 면적보다 더 작다[5]. 그런데 eFuse OTP는 eFuse에 수 십 mA의 프로그램 전류를 흘려주기 위해서 SL(Source Line) 구동회로의 구동 트랜지스터 사이즈가 크다. SL 구동회로의 구동 트랜지스터가 클수록 레이아웃 면적이 커진다. 기존의 4행 × 8열을 갖는 eFuse OTP는 eFuse의 큰 프로그램 전류를 공급해 주는 SL 구동회로를 매 열(column)마다 배치하므로 8개의 SL 구동회로가 차지하는 레이아웃 면적이 큰 문제점이 있다.

본 논문에서는 행의 개수가 열의 개수보다 작은 4행 × 8열의 셀 어레이를 갖는 eFuse OTP IP 설계에서 eFuse의 프로그램 전류를 공급하는 SL 구동 라인을 열 방향으로 라우팅 하는 대신 행 방향으로 라우팅 하므로 레이아웃 면적을 많이 차지하는 SL 구동회로 수를 8개에서 4개로 줄이는 셀 어레이 방식과 코어 회로를 제안하였다. 제안된 셀 어레이 방식과 코어 회로는 32비트 eFuse OTP IP의 레이아웃 면적을 줄일 수 있다. 그리고 수 백 ㎂ 이상의 큰 read 전류에 의해 blowing 되지 않은 eFuse가 EM(Electro-Migration) 현상에 의해 blowing되는 현상을 방지하기 위하여 RWL (Read Word-Line) 구동회로와 BL(Bit-Line) 풀-업 부하회로에 필요한 V2V(=2V±10%) 레귤레이터를 설계하였다.

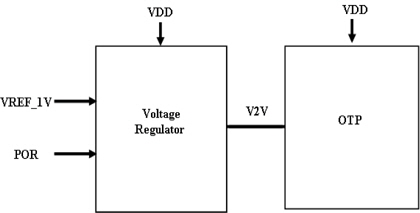

그림 3은 x-ray 라인 스캔 센서에 내장되는 V2V 전압 레귤레이터와 32비트 eFuse OTP 메모리 IP의 블록도를 보여주고 있다. V2V 레귤레이터는 VREF_1V의 기준 전압을 이용하여 2V±10%의 레귤레이션된 전압을 구동하는 회로이며, OTP IP의 RWL 구동회로와 BL 풀-업 부하회로에 사용된다.

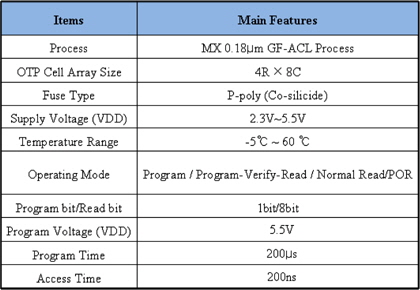

설계된 32비트 eFuse OTP IP의 주요 특징은 표 1과 같다. 공정은 매그나칩 반도체 0.18㎛ GF-ACL 공정을 이용하였으며, 셀 어레이는 4행 × 8열로 구성되어 있다. eFuse OTP 셀은 differential paired eFuse OTP 셀에 비해 셀 면적이 작은 듀얼 포트 eFuse OTP 셀을 사용하였 으며, eFuse 링크는 p-polysilicon을 사용하였다. 0.18㎛ GF-ACL 공정에서는 p-polysilicon eFuse가 n-polysilicon eFuse보다 blowing이 잘된다.

[표 1.] 32b eFuse OTP IP의 주요 특징.

32b eFuse OTP IP의 주요 특징.

동작모드는 프로그램 모드, read 모드와 PVR (Program-Verify-Read) 모드가 있다. 그리고 eFuse OTP 메모리의 프로그램 비트와 read 비트는 각각 1비트, 8비트이고 프로그램 시간은 200μs이다. 사용되는 전원전압은 VDD이고, V2V는 VDD 공급전압을 레귤레이션한 전압이다. VDD 전압은 프로그램 모드인 경우 eFuse 링크에 충분한 프로그램 파워를 공급하기 위해 5.5V가 사용되며, 읽기 모드인 경우 2.3~5.5V가 사용된다. 설계에 사용된 소자는 공정 비용을 줄이기 위해 1.8V의 로직 트랜지스터를 사용하지 않고 5V MOS 트랜지스터만을 사용하였다.

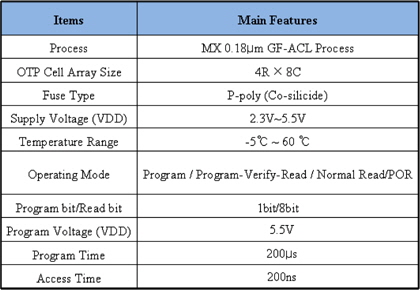

32비트 eFuse OTP 메모리 설계에 사용된 기존의 듀얼 포트 eFuse OTP 셀의 회로도는 그림 3(a)에서 보는 바와 같으며, 큰 프로그램 전류를 흘릴 수 있는 프로그램용 NMOS 트랜지스터(MN1)와 읽기 모드 전류를 줄일 수 있는 읽기용 NMOS 트랜지스터(MN2)가 각각 사용되고 있다. BL과 SL은 그림 4(a)에서 보는 바와 같이 모두 열 방향으로 향하고 있다. 그런데 그림 4(a)의 OTP 셀을 이용한 4행 × 8열을 갖는 eFuse OTP IP는 eFuse의 큰 프로그램 전류를 공급해 주는 SL 구동회로를 매 열마다 배치하므로 8개의 SL 구동회로가 차지하는 레이아웃 면적이 큰 문제점이 있다. 그래서 본 논문에서는 행의 개수가 열의 개수보다 작은 4행 × 8열의 셀 어레이를 갖는 eFuse OTP IP 설계에서 eFuse의 프로그램 전류를 공급하는 SL 구동 라인을 열 방향으로 라우팅 하는 대신 행 방향으로 라우팅 하므로 레이아웃 면적을 많이 차지하는 SL 구동회로 수를 줄이는 셀 어레이 방식과 코어 회로를 제안하였다. 제안된 셀 어레이 방식과 코어 회로는 32비트 eFuse OTP IP의 레이아웃 면적을 줄일 수 있다.

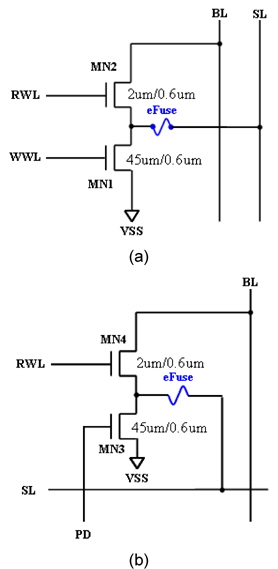

그림 4(b)는 제안된 듀얼 포트 eFuse OTP 셀 회로로 BL은 열 방향을 유지하지만 SL은 RWL과 같은 행 방향으로 라우팅 되어 있다. 그림 5는 제안된 듀얼 포트 eFuse OTP 셀의 레이아웃 이미지이며, 셀 사이즈는 8.51㎛ × 11.26㎛ (=95.8226㎛2)이다.

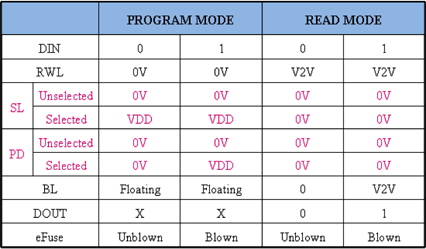

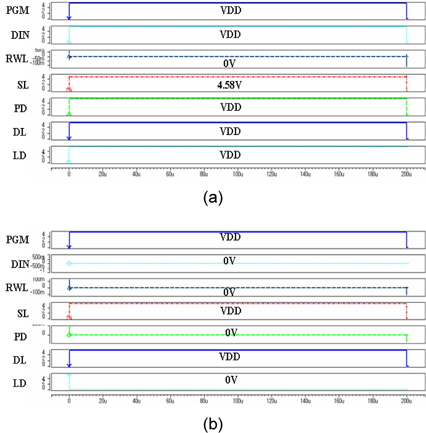

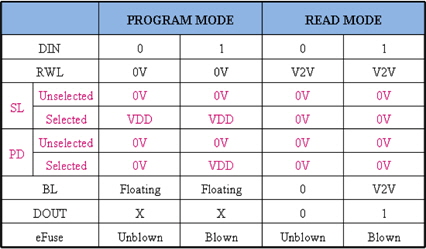

동작 모드별 eFuse OTP 셀의 바이어스 전압은 표 2에서 보는 바와 같다. 프로그램 모드에서 ‘1’로 프로그램되는 eFuse 셀의 SL과 PD(Program Data) 신호는 모두 VDD로 구동된다. 이와 같이 eFuse에 과전류가 흐르면 eFuse는 thermal rupture에 의해 blowing된다. 선택된 행의 SL은 VDD인 반면, 선택되지 않은 행의 SL은 0V를 유지한다. 그리고 DIN이 ‘1’인 경우 PD는 VDD를 구동하지만 DIN이 ‘0’인 경우 PD는 0V를 구동한다. 그래서 SL이나 PD 중 한 신호라도 0V인 OTP 셀의 eFuse 링크는 프로그램 전류가 흐르지 않으므로 blowing되지 않는다. Read 모드에서 선택된 RWL은 V2V를 구동하고 행 어드레스인 A[4:3]에 상관없이 모든 SL은 0V를 구동한다. ‘0’로 프로그램된 셀은 eFuse는 전도 상태이므로 BL에 0V를 출력하는 반면, ‘1’로 프로그램된 셀은 고저항 상태이므로 BL에 V2V를 출력한다.

동작 모드에 따른 셀 바이어스 조건

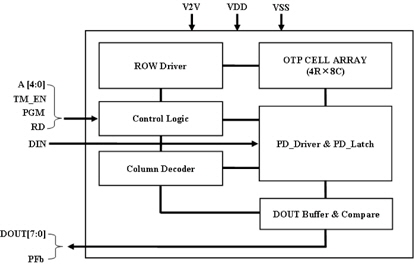

0.18μm GF-ACL 공정을 이용하여 설계한 32비트 eFuse OTP 메모리의 블록도는 그림 6에서 보는 바와 같이 4행 × 8열의 OTP 셀 어레이, 제어 신호(RD, PGM, TM_EN)에 따라 동작 모드에 적합한 내부 제어신호를 공급하는 제어 로직, 행 어드레스 A[4:3]을 디코딩하여 4개의 행 중 하나를 구동해주는 row driver, 열 어드레스 A[2:0]를 디코딩하여 프로그램 되는 8개의 열 중 한열을 선택해주는 PD driver 회로, 프로그램 데이터를 저장하는 프로그램 데이터 래치(PD latch) 회로, BL의 데이터를 읽어내기 위한 DOUT 버퍼, 그리고 프로그램 데이터 래치에 저장된 프로그램 데이터 LD[7:0]와 DOUT 버퍼의 읽어낸 데이터 DOUT[7:0]이 일치하는지 비교해주는 비교회로로 구성되어 있다. LD[7:0]와 DOUT [7:0]를 해당 비트끼리 비교하였을 때 모든 비트가 일치하는 경우는 정상적으로 프로그램 되었으므로 PFb 신호는 ‘1’을 출력하고, 8비트 중 한 비트 이상이 불일치하면 ‘0’를 출력한다. TM_EN(Test Mode ENable) 신호는 PVR 모드와 read 모드를 구분해 준다.

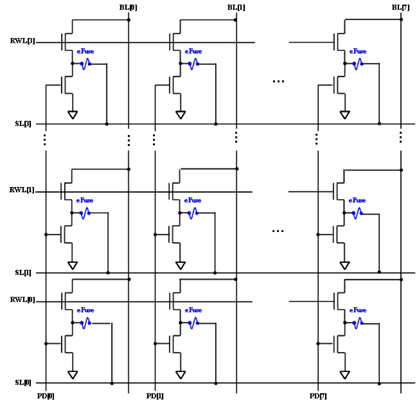

그림 7은 4행 × 8열의 제안된 셀 어레이 회로도를 보여주고 있다. RWL[3:0], SL[3:0]와 VSS는 행 방향이고, PD[7:0]과 BL[7:0]는 열 방향으로 라우팅 되어 있다.

eFuse OTP의 프로그램 동작은 어드레스 A[4:0]와 입력 데이터 DIN을 먼저 인가한 상태에서 PGM 신호가 0V에서 VDD로 활성화 되면 선택되는 eFuse OTP 메모리 셀은 프로그램 된다. 그리고 프로그램 모드에서 프로그램 입력 데이터 DIN은 eFuse OTP 메모리를 프로그램 하는데 사용할 뿐만 아니라 프로그램 데이터 래치 회로에 래치된다. 읽기 동작은 RD 신호를 VDD로 활성화시키면 8비트의 출력 데이터가 액세스 시간이 지난이후 DOUT[7:0] 포트로 출력된다. 이때 PGM 신호는 0V를 유지해야 된다. 한편 eFuse OTP 메모리 IP는 패키지 상태에서 정상적으로 프로그램 되었는지 테스트가 가능하도록 설계가 되어야 한다. 프로그램 모드를 수행한 이후 연속으로 PVR 모드를 수행하면 dynamic pseudo NMOS 로직회로를 이용한 프로그램 데이터 비교회로는 프로그램 데이터 래치 회로에 래치된 프로그램 데이터와 read 모드에서 선택된 셀의 read 데이터를 비교하여 PFb(Pass Fail bar) 핀으로 비교 결과를 확인할 수 있다[6]. 그래서 본 논문에서는 PVR 모드에서 프로그램 데이터와 read 데이터를 비교하여 PFb 핀으로 비교 결과를 출력하도록 설계하였다.

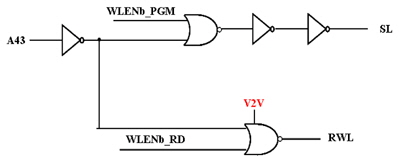

그림 8의 제안된 행 구동회로는 프로그램 모드로 진입하게 되면 WLENb_PGM 신호가 0V가 되며, 행 어드레스인 A[4:3]을 디코딩하여 선택되는 SL만 VDD 전압으로 구동되고 선택되지 않은 SL은 0V를 유지하도록 한다. 이때 WLENb_RD 신호는 프로그램 모드에서 VDD를 유지하므로 RWL은 0V를 유지한다. 그리고 read 모드와 PVR 모드에서 선택된 RWL은 V2V로 구동되고 선택되지 않은 RWL은 0V를 유지한다. 2.3V~5.5V의 넓은 동작 전압 범위를 갖는 eFuse OTP를 설계하는 경우 2.3V의 저전압 VDD 조건에서 post-program 저항이 수 십 ㏀ 정도인 eFuse를 데이터 ‘1’로 센싱하도록 BL 풀-업 부하를 사용하게 되면 5.5V의 VDD에서 프로그램되지 않은 eFuse 셀을 read할 때 RWL을 0V에서 VDD로 활성화되면서 blowing되지 않은 eFuse를 통해 큰 전류가 흐른다. 그래서 blowing 되지 않은 eFuse는 EM 현상에 의해 blowing되는 현상이 일어날 수 있다. 그래서 RWL과 BL 풀-업 부하는 넓은 동작 전압 범위를 갖는 VDD를 사용하는 대신 전압 변동이 작은 V2V를 사용하여 blowing 되지 않은 eFuse에 흐르는 전류는 줄여 eFuse OTP의 신뢰성을 확보하였다[5]. 본 논문에서는 blowing 되지 않은 eFuse가 EM 현상에 의해 blowing되는 현상을 방지하기 위하여 RWL 구동회로와 BL 풀-업 부하회로에 필요한 V2V 레귤레이터 회로를 설계하였다.

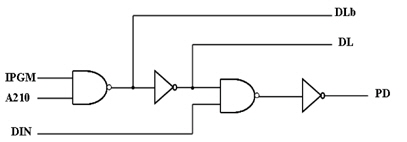

그림 9의 PD 구동 회로는 프로그램 모드에서 행 어 드레스인 A[2:0]을 디코딩하여 프로그램 되는 열의 DL(Data Latch) 신호만 VDD 전압을 공급한다. 선택되는 열의 PD(Program Data)는 DIN이 VDD인 경우 VDD 전압을 공급하고, DIN이 0V인 경우 0V로 구동한다. 한편 프로그램 되지 않는 SL 신호는 0V를 유지하도록 한다. 그리고 읽기 모드에서는 IPGM 신호가 0V이므로 PD는 0V를 구동하도록 한다.

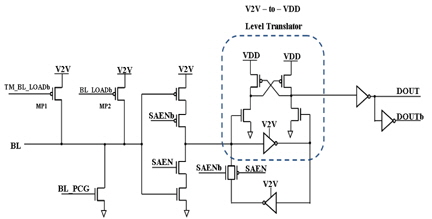

그림 10은 제안된 DOUT 버퍼 회로로 read 모드와 PVR 모드에서 BL 프리차지 신호인 BL_PCG 신호에 의해 BL은 0V로 프리차징 된다. OTP 셀의 RWL 전압이 V2V로 활성화되면 BL 풀-업 부하 트랜지스터(MP1 또는 MP2)에 의해 BL은 V2V로 풀-업 된다. eFuse OTP 메모리 셀의 데이터가 BL에 충분히 전달되면 DOUT 버퍼는 SAENb(Sense Amplifier ENable bar) 신호가 0V로 활성화된 뒤 V2V 또는 0V인 BL 전압을 센싱하여 DOUT 포트로 읽은 데이터를 출력한다. 그런데 eFuse OTP 셀은 데이터 retention 시간인 10년 동안 프로그램된 eFuse 링크의 저항이 줄어드는 경우를 고려한 가변 풀-업 부하 회로[7]를 사용하였다. eFuse를 프로그램한 후 PVR 모드에서는 그림 10의 가변 풀-업부하 트랜지스터 중 MP1만 ON시켜 eFuse 저항이 정상적으로 프로그램 되었는지 테스트한다. 그리고 read모드에서는 MP1보다 풀-업 저항이 작은 MP2만 ON시켜 프로그램된 eFuse 저항이 낮게 변동하더라도 BL을 풀-업시켜 정상적인 ‘1’ 데이터로 센싱하도록 한다. 그래서 PVR 모드와 read 모드에서 센싱 가능한 eFuse 저항의 차이 값이 데이터 retention 시간동안 DOUT 버퍼에서의 BL 센싱 마진 저항이 된다.

PMIC용 OTP 설계에서는 VDD_PD 신호는 파워-업 시 V2V-to-VDD 레벨 translator 회로에서 V2V가 전압 레귤레이터에서 만들어지기 이전에 레벨 translator에서 단락 회로 전류가 흐르는 것을 방지하기 위하여 필요하다[5]. 그러나 라인 스캔 센서에서는 VDD가 파워-업 되면서 V2V는 동시에 만들어지므로 V2V-to-VDD 레벨 translator 회로에서 VDD_PD 신호를 이용한 단락 회로 전류를 차단할 필요는 없다.

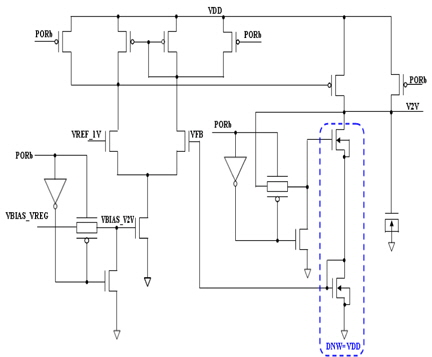

그림 11은 그림 3에서 보여지는 V2V 레귤레이터 회로를 보여주고 있으며, V2V의 기준전압인 VREF_1V는 1V가 걸린다. VBIAS_VREG는 바이어스 전류인 IREF_2㎂(=2㎂) 전류가 흐르는 NMOS 다이오드의 VGS(Gate-Source Voltage) 전압이다. V2V 레귤레이터 회로는 구동전압인 V2V와 VSS 사이에 2개의 NMOS 다이오드가 직렬로 연결되어 있으므로 정상상태에서 VREF_1V 전압과 VFB 전압은 같아진다. VREF_1V 전압과 VFB 전압이 같아지면 V2V 전압은 VREF_1V 전압의 2배인 2V를 구동하게 된다. V2V의 리플 전압을 줄이기 위해 V2V와 VSS 사이에 NMOS 전하 저장 커패시터를 두고 있다.

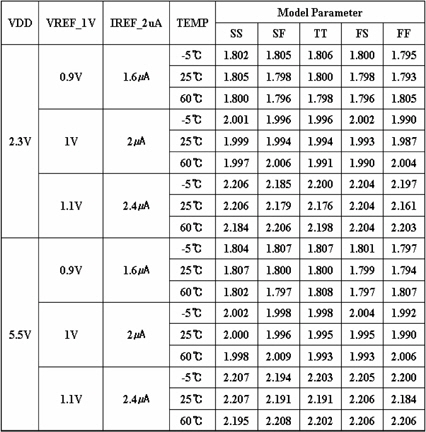

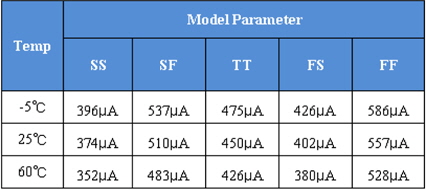

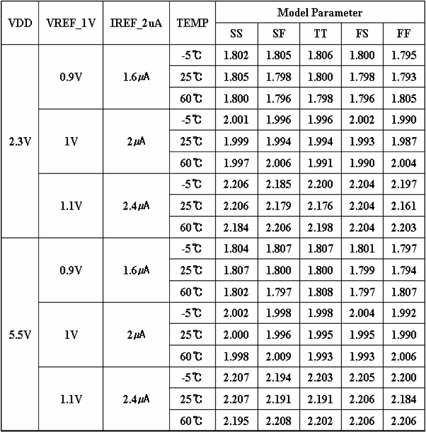

본 논문에서는 매그나칩 반도체 0.18㎛ GF-ACL 공정 기반의 32비트 eFuse OTP 메모리를 설계하였다. 표 3은 공급전압인 VDD, 기준전압인 VREF_1V, 바이어스 전류인 IREF_2㎂, 온도, 모델 파라미터별 전압 레귤레이터인 V2V의 모의실험 결과이다. VDD는 각각 2.3V와 5.5V, VREF_1V는 각각 0.9V, 1V, 1.1V이며, 온도는 각각 -5℃, 25℃, 60℃이다. 모델 파라미터는 각각 SS, SF, TT, FS, FF이다. 모의실험 결과 V2V 전압은 각각 1.795V~2.208V로 목표 전압인 1.8V~2.2V에 근접한 것을 볼 수 있다.

[표 3.] 시뮬레이션 조건에 따른 V2V 모의실험결과

시뮬레이션 조건에 따른 V2V 모의실험결과

2.3V~5.5V의 넓은 동작전압 영역을 갖는 eFuse OTP IP를 설계하는 경우 2.3V의 저전압 VDD 조건에서 post-program 저항이 수 십 ㏀ 정도인 프로그램된 eFuse를 데이터 ‘1’로 센싱하도록 BL 풀-업 부하를 사용하게 되면 5.5V의 VDD에서 프로그램되지 않은 eFuse 셀을 읽을 때 RWL 전압을 VDD로 활성화되면서 blowing되지 않은 eFuse를 통해 큰 전류가 흐르게 된다. 이 때 큰 전류에 의해 blowing 되지 않은 eFuse는 EM 현상에 의해 blowing되는 현상이 일어날 수 있다.

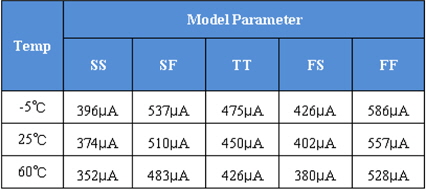

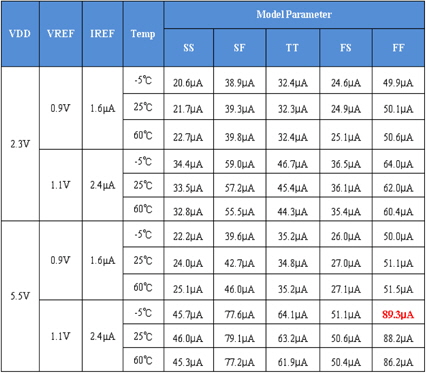

표 4는 프로그램 되지 않은 eFuse 링크의 read 전류에 대한 기존 회로의 모의실험 결과를 보여주고 있으며, FF 모델 파라미터, -5℃에서의 read 전류는 586㎂로 크게 흐르는 것을 볼 수 있다. 그리고 표 5는 제안된 회로의 프로그램 되지 않은 eFuse 링크의 read 전류에 대한 실험 결과를 보여주고 있다. 그래서 그림 8과 그림 10에서의 회로를 이용하여 RWL과 BL 풀-업 부하는 VDD를 사용하는 대신 전압 변동이 작은 V2V를 사용하여 blowing 되지 않은 eFuse에 흐르는 전류를 89.3㎂ 이내로 줄여 eFuse OTP의 신뢰성을 확보하였다.

[표 4.] 프로그램되지 않은 eFuse 링크의 read 전류에 대한 기존 회로의 모의실험 결과

프로그램되지 않은 eFuse 링크의 read 전류에 대한 기존 회로의 모의실험 결과

[표 5.] 프로그램되지 않은 eFuse 링크의 read 전류에 대한 모의실험 결과

프로그램되지 않은 eFuse 링크의 read 전류에 대한 모의실험 결과

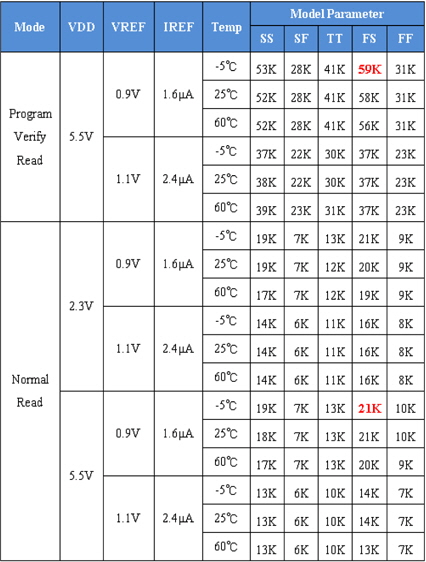

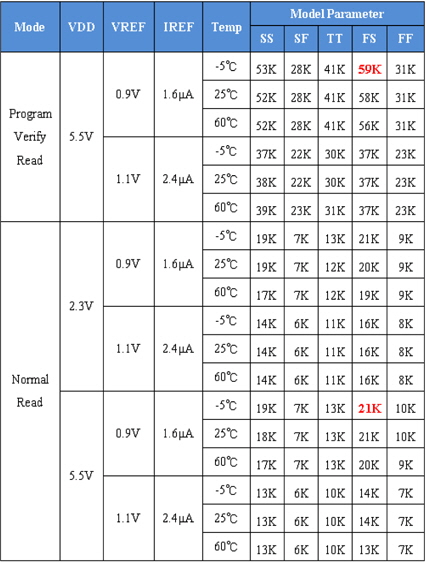

표 6은 프로그램된 eFuse 링크의 센싱 저항에 대한 모의실험 결과이다. 가변 풀-업 부하 회로를 사용하므로 VDD=5.5V, VREF=0.9V, FS(Fast NMOS, Slow PMOS) 모델 파라미터, -5℃의 PVR 모드와 read 모드에서의 eFuse 센싱 저항은 각각 59kΩ, 21kΩ으로 모의실험 되었다. 이 경우 프로그램된 eFuse 저항이 10년 동안 38kΩ 정도 떨어지지 않는 이상 정상적으로 센싱이 가능하다. 그리고 PVR 모드의 VDD 전압은 eFuse OTP의 한 바이트를 프로그램한 뒤 바로 PVR 모드를 수행해야 하므로 프로그램 모드의 VDD 전압인 5.5V를 사용하였다.

[표 6.] 프로그램된 eFuse 링크의 센싱 저항에 대한 모의실험 결과

프로그램된 eFuse 링크의 센싱 저항에 대한 모의실험 결과

그림 12는 프로그램 모드의 모의실험 결과이다. A[4:0]를 먼저 인가한 상태에서 PGM 신호가 high로 활성화 되면 DIN이 ‘1’인 경우 그림 12(a)에서 보는 바와 같이 선택된 eFuse 셀의 SL와 PD는 모두 high가 되어 그림 4(b)의 ON이 되어있는 MN3를 통해 프로그램 전류가 흘러서 eFuse 링크는 blowing된다. 반면 DIN이 ‘0’인 경우 그림 12(b)에서 보는 바와 같이 SL은 high이지만 PD는 low가 되어 MN3는 OFF되어 프로그램 전류가 흐르지 않는다. eFuse 링크에 프로그램 전류가 흐르지 않으면 blowing되지 않는다.

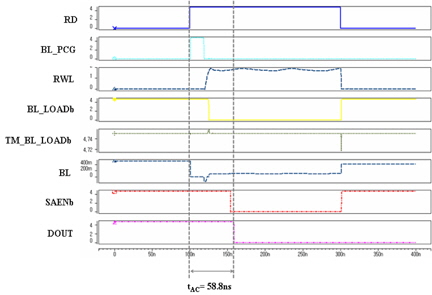

그림 13은 32비트 eFuse OTP 메모리에 대한 read 모드에서의 모의실험 결과이다. RD 신호가 활성화 되면 RWL 신호가 high로 되고, BL에 eFuse OTP 셀의 데이터가 전달된 뒤 SAENb 신호에 의해 BL의 데이터는 DOUT 포트로 출력된다. VDD=2.3V, VREF=0.9V, Temp=60℃에서 액세스 시간(tAC)은 58.8ns이다.

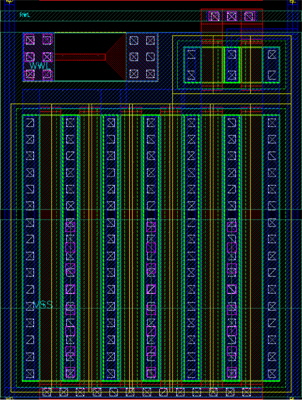

설계된 4행 × 8열의 32비트 eFuse OTP IP의 레이아웃 면적은 그림 14에서 보는 바와 같이 120.1㎛ × 127.51㎛(=0.01531㎜2)로 기존의 eFuse OTP IP의 면적인 187.065㎛ × 94.525㎛(=0.01768㎜2)보다 13.4% 더 작은 것을 확인하였다.

x-ray 라인 스캔 센서는 아날로그 회로를 트리밍하기 위해서는 소용량의 비휘발성 메모리를 필요로 한다. x-ray 라인 스캔 센서에 내장되는 비휘발성 메모리는 추가 공정이 필요 없는 로직 공정 기반 설계가 가능한 eFuse OTP 메모리가 많이 사용되고 있다.

본 논문에서는 행의 개수가 열의 개수보다 작은 4행 × 8열의 셀 어레이를 갖는 eFuse OTP IP 설계에서 eFuse의 프로그램 전류를 공급하는 SL 구동 라인을 열 방향으로 라우팅 하는 대신 행 방향으로 라우팅 하므로 레이아웃 면적을 많이 차지하는 SL 구동회로 수를 8개에서 4개로 줄이는 셀 어레이 방식과 코어 회로(SL 구동회로와 DOUT 버퍼 회로)를 제안하였다. 제안된 셀 어레이 방식과 코어 회로는 32비트 eFuse OTP IP의 레이아웃 면적을 줄일 수 있었다.

그리고 RWL 구동회로와 BL 풀-업 부하회로에 VDD를 사용하는 대신 전압 변동이 작은 V2V를 사용하여 blowing 되지 않은 eFuse에 흐르는 전류를 89.3㎂ 이내로 줄여 eFuse OTP의 신뢰성을 확보하였다. 설계된 4행 × 8열의 32비트 eFuse OTP IP의 레이아웃 면적은 120.1㎛ × 127.51㎛ 로 기존의 eFuse OTP IP의 면적인 187.065㎛ × 94.525㎛보다 13.4% 더 작은 것을 확인하였다.

![x-ray 라인 스캔 센서의 블록도[1]](http://oak.go.kr/repository/journal/14093/HOJBC0_2014_v18n8_1914_f001.jpg)

![ASP 회로의 블록도[1]](http://oak.go.kr/repository/journal/14093/HOJBC0_2014_v18n8_1914_f002.jpg)