In this paper, a systematic demapping algorithm for three-dimensional (3-D) lattice signal constellations is presented. The algorithm consists of decision of an octant, computation of a distance from the origin, and determination of the coordinates of a symbol. Since the algorithm can be extended systematically, it is applicable to the larger lattice constellations. To verify the algorithm, 3-D signal transmission systems with field programmable gate array (FPGA) and Matlab® are implemented. And they are exploited to carry out computer simulation. As a result, both hardware and software based systems produce almost the same symbol error rates (SERs) in an additive white Gaussian noise (AWGN) environment. In addition, the hardware based system implemented with an FPGA generates waveforms of 3-D signals and recovers the original binary sequences perfectly. Those results confirm that the algorithm and the implemented 3-D transmission system operate correctly.

다차원 신호성상도(multidimensional signal constellation)를 이용한 디지털 통신시스템에 대한 연구들이 꾸준히 수행되어 왔다[1-3]. 특히, 광통신 분야에서는 3차원 변조를 이용하는 전송시스템에 대한 관심이 증가되고 있다[4-6]. 신호성상도(signal constellation) 상의 심볼(또는 신호점) 수와 이들의 평균 전력이 동일한 조건에서 3차원 신호성상도는 2차원 성상도에 비하여 훨씬 증가된 최소 유클리드 거리(minimum Euclidean distance)를 가지는 것으로 알려진 바 있다[1, 2, 7]. 이에 따라 최근에는 3차원 전송시스템도 차세대 디지털 통신을 위한 유용한 기술 가운데 하나로 인식되고 있다.

3차원 신호 전송시스템에 대한 대부분의 기존 연구들은 달성 가능한 오류 성능이나 전송율 등에 대한 이론적인 분석을 주로 다루고 있다[6-8]. 이에 따라 실제적인 시스템의 구현과 이를 위한 세부 기능블럭의 구현에 대한 연구는 그 중요성에 비하여 소홀하게 다루어진 경향이 있다. 특히, 현실적인 3차원 전송시스템의 실현을 위한 구체적인 모델에 대한 연구 결과는 현재까지 보고된 바 없는 것으로 조사되었다.

본 논문에서는 3차원 신호성상도를 이용하는 전송시스템을 위한 체계적인 역사상(demapping) 알고리즘을 제안한다. 이는 두 개의 세부 기능으로 구성되어 있으며, 첫 단계에서는 수신 심볼이 포함된 8분 공간(octant) 이 결정되고 두 번째로는 심볼의 정확한 좌표가 계산된다. 제안된 알고리즘은 신호성상도의 구조에 따라 다단 알고리즘으로의 체계적인 확장이 가능하므로 더 큰 성상도에도 적용이 가능한 장점이 있다. 제시된 알고리즘 의 검증을 위하여 본 논문에서는 field programmable gate array (FPGA)을 이용한 하드웨어 기반 3차원 전송시스템과 상용 소프트웨어를 이용한 시스템을 구현하여 모의실험에 사용하였다. 여기서는 하드웨어 표현 언어(hardware description language, HDL)을 이용하여 핵심 기능모듈을 구현하였으며, 처리 능력 향상을 위하여 고정 소수점형수 형식(fixed-point number format)을 이 용하였다. 또한 송신기에서 이진 부호어를 3차원 신호 성분으로 사상시키기 위한 방법으로 조견표(look-up table)을 이용하였다. 그 결과, 하드웨어와 소프트웨어 기반 3차원 신호 전송시스템들은 거의 동일한 심볼오율 (symbol error rate, SER)을 가지는 것으로 나타났다. 레지스터 전사 레벨(register transfer level, RTL) 실험에서 설계된 시스템들은 이진 부호열의 3차원 신호변환과 수신된 심볼로부터 원래 이진열 복원이 정확하게 수행됨을 확인할 수 있었다. 따라서 제안된 역사상 알고리즘과 이를 기반으로 설계된 3차원 신호 전송시스템이 정확하게 동작하는 것으로 판단된다.

본 논문의 구성은 다음과 같다. II장에서는 3차원 신호 전송시스템을 간략하게 소개한다. III장에서는 제안된 역사상 알고리즘을 자세히 설명한다. IV장에서는 성능 분석을 위한 하드웨어 및 소프트웨어 구현 방법을 제시한다. 그리고 이들을 기반으로 한 모의실험 결과와 분석도 제시된다. 끝으로 결론과 향후 추가 연구분야를 V장에 제시한다.

이진 부호열

임의의 3차원 신호는 신호점의 좌표를 이용하여

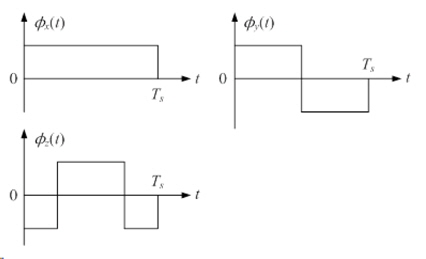

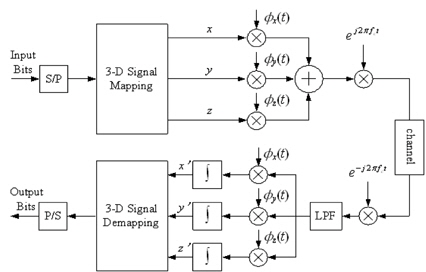

3차원 신호 전송시스템의 단순화된 블록도를 그림 3에 나타내었다. 여기서 S/P와 P/S는 직병렬변환기(serial-to-parallel converter)와 병직렬변환기(parallel-to-serial converter)를 각각 나타내고, LPF는 저역통과필터(low pass filter)이다. 정보원에서 발생된 이진 정보열은 신호 사상 블록에서 3차원 심볼로 변환되고 Gram-Schmidt 직교화 과정에 의하여 생성된 직교 기저함수에 따라 다음과 같이 기저대역 신호파형으로 변환된다.

따라서 반송주파수

가 된다. 여기서

수신기 전단에서 반송대역 신호를 기저대역으로 주파수 하향변환(frequency down-conversion)시키면 가산성 백색 가우시안 잡음(additive white Gaussian noise, AWGN) 환경에서 수신신호는

로 나타낼 수 있다. 여기서 잡음신호는

로 표현되는 가우시안 랜덤 프로세스이다.

3차원 신호 역사상기는 복원된 신호

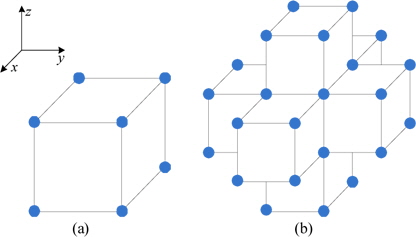

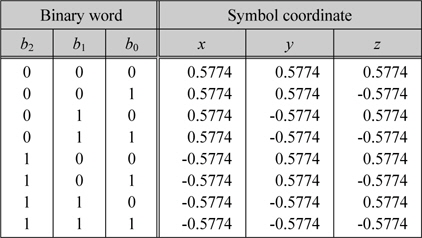

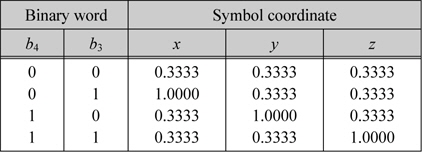

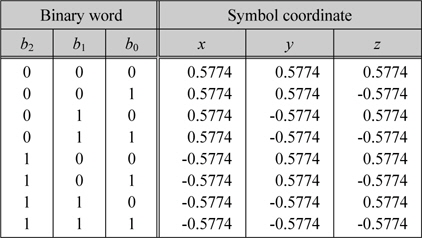

다양한 형태의 3차원 격자형 신호성상도를 전송시스템에 효과적으로 적용하기 위해서는 송신기의 사상과 수신기의 역사상 알고리즘이 융통성 있도록 설계되어야 한다. 그림 1(a)의 구조는 3차원 격자형 성상도들의 기본적인 요소이다. 여기서 신호점들은 원점을 중심으로 대칭 분포하고, 심볼 당 비트수가 성상도의 차원과 동일하므로 이진 단어(binary word)의 각 비트는 심볼의 각 축방향 좌표의 부호(sign)에 따라 결정된다. 8진성상도에서 발생 가능한 이진 단어들과 심볼 좌표들의 관계를 표 1에 나타내었다. 여기서

[표 1.] 8진 성상도를 위한 이진 단어와 심볼 좌표의 관계

8진 성상도를 위한 이진 단어와 심볼 좌표의 관계

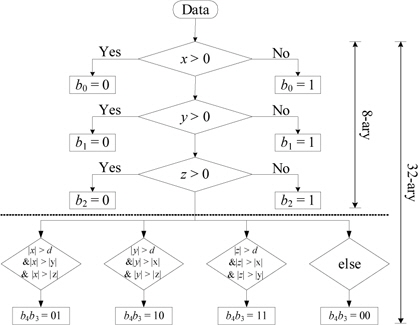

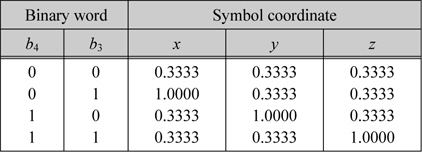

그림 1(b)에 나타낸 32진 격자형 성상도도 원점에 대하여 대칭적인 구조를 가지며, 모든 심볼들은 두 개의 동심구(concentric sphere) 표면에 분포한다. 성상도의 평균전력이 1이 되도록 정규화시키면 내부 구의 반지름은 약 0.5774이고 외부 구의 반지름은 약 1.1055가 된다. 각 8분 공간에는 네 개의 신호점이 있으며, 이들 가운데 하나는 내부 구에 나머지 세 개는 외부 구의 표면에 분포한다. 따라서 역사상 알고리즘은 2 단계로 구성할 수 있다. 첫 단계에서는 수신된 심볼이 존재하는 8분 공간을 결정한다. 두 번째에서는 수신 심볼과 원점과의 거리를 계산하여 좌표를 결정한다. 32진 성상도의 심볼 을 나타내는 5비트 이진 단어를

[표 2.] 32진 성상도에서 상위 두 비트의 사상을 위한 조견표.

32진 성상도에서 상위 두 비트의 사상을 위한 조견표.

흐름도의 상위 부분은 8진 성상도에 대한 역사상 알고리즘이고, 전체 흐름도는 32진 신호성상도를 역사상 시키는 과정이다.

제안된 알고리즘의 검증을 위하여 FPGA를 이용한 하드웨어 기반 3차원 전송시스템과 상용 소프트웨어를 이용한 시스템을 구현하여 모의실험을 수행하고, 그 결과를 비교하였다. 모든 기능 모듈(function module)은 가장 널리 사용되고 있는 Verilog 하드웨어 표현 언어를 이용하여 설계하였으며[10-12], 연산 과부하를 피하기 위하여 고정 소수점형 수 형식을 이용하여 산술연산을 수행하였다.

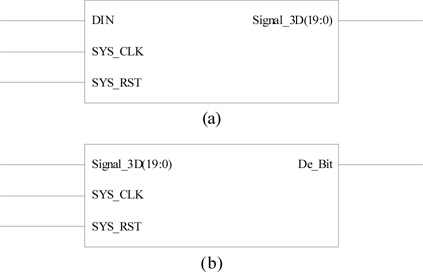

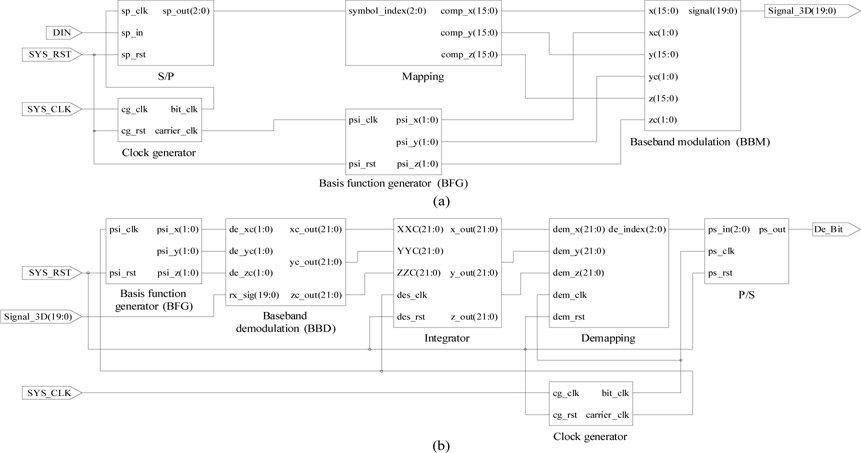

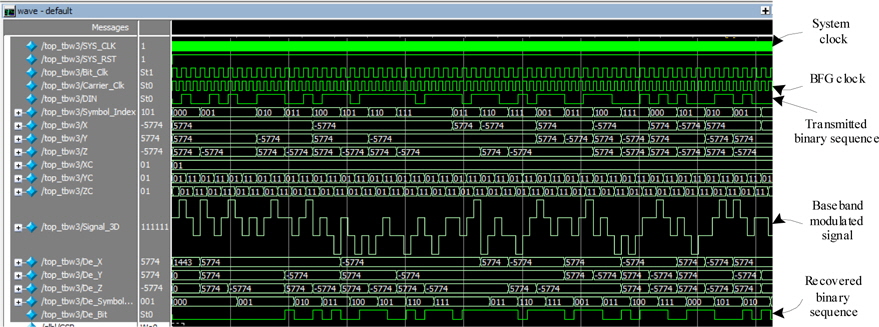

전체적인 시스템은 하향식(top-to-down)으로 설계가 진행되었다. 송수신기의 상위 모듈에 대한 레지스터 전사 레벨 계통도를 그림 5에 나타내었다. 여기서 DIN은 의사 랜덤 이진열(pseudo-random binary sequence) 발생기에서 생성된 데이터의 입력 포트이다. SYS_CLK와 SYS_RST는 외부 시스템 클럭과 리셋 신호 포트를 각각 나타낸다. Signal_3D는 식 (1)에 따라 생성된 기저 대역 3차원 신호를 송신기에서 출력하는 포트이고 수신기에서는 주파수 하향 변환된 3차원 수신신호의 입력 포트이다. 3차원 신호는 20 비트 길이의 이진열로 표현되며, 이 가운데 16 비트는 심볼 좌표를 고정 소수점형수 형식으로 표현하는데 이용된다. 수신 심볼로부터 복구된 이진열은 De_Bit 포트를 통하여 출력된다.

그림 5에 나타낸 시스템에 대한 하위 모듈 상세 계통도를 그림 6에 나타내었다. 송신기는 클럭발생기, 기저함수발생기(basis function generator, BFG), 직병렬변환기, 사상기, 기저대역 변조기(baseband modulation) 등 으로 구성되어 있다. 클럭발생기는 직병렬변환기와 기저대역 변조기를 제어하는 클럭 펄스열을 발생한다. 3차원 심볼의 좌표를 나타내는 계수는 읽기전용 기억장치(read-only memory)에 저장되며 이진열을 3차원 신호로 변환시키는 사상기에서 사용된다. 기저대역 변조모듈은 식 (1)에 나타낸 기저대역 신호를 발생시킨다.

수신기를 구성하는 주요 모듈은 클럭발생기, 기저대역 복조기, 적분기와 역사상기 등이다. 이와 같은 기능 모듈에서 사용되는 파라미터들은 신호성상도의 구조와 크기에 따라 달라진다. 송수신기를 구성하는 모든 기능 모듈은 하드웨어 모의실험 chip으로 합성되며, 본 논문에서는 Spartan 3E 계열을 이용하였다.

FPGA를 이용한 하드웨어 기반 3차원 신호 전송시스템에서 발생, 송수신, 복구되는 신호 파형 실험 결과를 그림 7에 나타내었다. 여기서는 8진 성상도가 사용되 다. 그 결과, 식 (1)에 나타낸 바와 같이 심볼의 좌표가 가중치로 적용되는 직교 기저함수의 합으로 표현되는 3차원 신호 파형(baseband modulated signal)이 정확하게 발생되는 것을 확인할 수 있다. 또한 정보원에서 발생된 이진열은 약간의 시간지연과 함께 수신기에서 정확하게 복구되는 것도 관측할 수 있다. 따라서 제안된 역사상 알고리즘은 FPGA로 구현된 3차원 전송시스템에서 정상적으로 동작하는 것으로 판단된다.

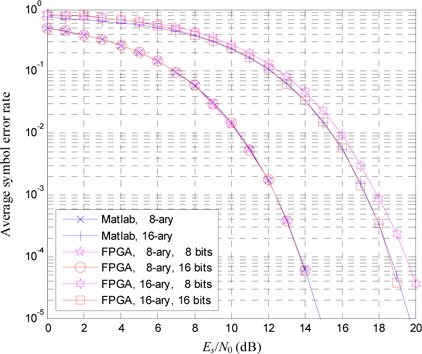

제안된 알고리즘과 구현된 하드웨어 기반 전송시스템을 검증하기 위한 다른 방법으로 신뢰성 있는 상용소프트웨어를 이용하여 3차원 전송시스템을 구현하고 모의실험을 수행하여 얻은 결과들을 비교하였다. 상용소프트웨어로는 통신 및 신호처리 분야에서 가장 광범위하게 사용되고 있는 Matlab®을 이용하였으며, 평균이 0이고 분산이 σ2인 가산성 백색 가우시안 잡음 채널을 이용하였다. 두 시스템에 대한 실험을 통하여 얻은 평균 심볼오율(symbol error rate, SER)을 그림 8에 나타내었다. 여기서 전체 심볼수는

8진 신호성상도를 이용하는 경우 고정 소수점형 수 형식을 표현하는 비트 길이에 상관없이 구현된 두 시스템은 거의 동일한 심볼 오류 성능을 가지는 것으로 나타났다. 이에 비하여 32진 성상도의 경우 8비트 길이 수 형식을 이용하여 구현된 하드웨어 시스템은 16비트 길이 수 형식이 적용된 것보다 심볼오율

본 논문에서는 3차원 격자형 신호성상도를 위한 역사상 알고리즘이 제안되었다. 제안된 알고리즘은 체계적인 확장이 가능함을 보였으며, 이는 약간의 변형을 통하여 더 큰 신호성상도에도 적용이 가능함을 의미한다. FPGA를 이용한 하드웨어 기반 3차원 신호 전송시스템과 소프트웨어를 이용한 시스템을 구현하여 제안된 알고리즘을 검증한 결과 3차원 신호 파형의 발생과 이진 데이터열의 발생/복구가 정확하게 이루어지는 것을 확인할 수 있었다. 또한 구현된 두 시스템은 거의 동일한 심볼오율을 가지는 것으로 나타났다. 따라서 제안된 역사상 알고리즘과 이를 적용하여 구현된 3차원 전송시스템은 정상적으로 동작하는 것으로 판단된다.

향후 게이트 레벨로 확장된 실제적인 하드웨어 테스트베드를 구현함으로써 3차원 신호 전송시스템의 신뢰성 검증과 초고속 디지털 통신시스템에의 적용 가능성에 대한 연구가 필요한 것으로 사료된다.