A hardware implementation of phase calculator for extracting 3D depth image from TOF(Time-Of-Flight) sensor is described. The designed phase calculator adopts redundant binary number systems and a pipelined architecture to improve throughput and speed. It performs arctangent operation using vectoring mode of DCORDIC(Differential COordinate Rotation DIgital Computer) algorithm. Fixed-point MATLAB simulations are carried out to determine the optimal bit-widths and number of iteration. The phase calculator has ben verified by FPGA-in-the-loop verification using MATLAB/Simulink. A test chip has been fabricated using a TSMC 0.18-㎛ CMOS process, and test results show that the chip functions correctly. It has 82,000 gates and the estimated throughput is 400 MS/s at 400Mhz@1.8V.

3차원 영상을 얻기 위해 가장 기본적으로 사용되는 방법은 양안식 카메라를 사용하는 스테레오 비전 시스템이다. 이 방법은 레이저, 초음파와 같이 거리 측정을 위한 다른 장비 없이 고해상도의 거리 영상을 얻을 수 있는 장점을 갖는다. 그러나 스테레오 영상을 이용하여 깊이를 정확히 측정하기 위해서는 알고리듬이 복잡하고 시간이 오래 걸리는 단점이 있다. 또한 물체에 의해 가려져 한쪽에서만 보이거나 무늬가 없어 깊이를 찾기가 어려운 영역에서는 장면의 깊이를 추정하기 어렵다[1, 2].

지난 몇 년간 학계에서는 TOF(Time-Of-Flight) 센서를 이용한 거리 영상 획득 방법에 대해 관심이 점점 더 커져, 그에 따라 실시간 거리 영상 시스템에 대한 연구가 활발히 진행되고 있다[3-5]. TOF의 기본 원리는 센서에서 방출된 빛이 대상 물체에 반사되어 돌아오는 시간을 계산하여 각 화소별로 장면의 대응점까지의 깊이를 측정하는 것이다. 3차원 영상처리용 TOF 카메라는 장면의 깊이 정보를 직접 측정하여 기존 스테레오 정합방법의 취약점을 보완할 수 있다. 아직 TOF 비전 분야는 SV 시스템에 비하여 해상도가 낮고, 센서에 주로 사용되는 적외선 신호의 특성으로 인한 제약이 있지만, 로봇, 자동차, 의료, 제스처 인식 등 다양한 분야의 어플리케이션에 대해 TOF 카메라가 생산, 사용되고 있다. 특히 자동차 산업에서 안전에 대한 관심의 증가로 TOF시장은 더욱 커질 것으로 예상되며, TOF 시장이 발전하기 위해서는 센서에서 얻어지는 많은 정보를 실시간으로 처리할 수 있는 효율적인 하드웨어 연구가 동반되어야 할 것이다.

본 논문에서는 3D TOF 센서용 깊이 정보를 고속으로 계산하기 위한 하드웨어를 DCORDIC(Differential COordinate Rotation DIgital Computer) 알고리듬[6] 기반의 위상연산 회로로 구현하였다. 설계된 위상 연산기의 HDL 모델을 MATLAB/Simulink와 FPGA가 연동된 FPGA-in-the-loop 검증 환경을 통해 하드웨어 검증을 하였으며, TSMC 0.18-㎛ CMOS 공정으로 테스트 칩을 제작하고 성능을 평가 하였다.

본 논문은 다음과 같이 구성된다. Ⅱ장에서는 TOF 거리 연산의 기본원리를 간략히 설명하고, Ⅲ장에서 는 DCORDIC 알고리듬에 대해 소개한다. Ⅳ장에서는 DCORDIC 기반 위상 연산기의 하드웨어 구조와 회로 설계에 대해 설명하고, 설계된 위상 연산기의 설계 검증 및 성능 평가, 그리고 테스트 칩 평가에 대해 Ⅴ장에서 기술하며, Ⅵ장에서 결론을 맺는다.

TOF 센서를 이용한 깊이 정보 추출의 기본원리는 다음과 같다. TOF 센서 시스템의 송신부에서 특정 주파수(

여기서

식 (2)에 따르면 장면의 깊이 정보를 얻기 위해서는 반드시 반사된 빛의 위상 변화를 알아야 한다. Jongenelen의 연구[3]를 참고하면, TOF 센서에서는 픽셀 강도 데이터가 들어오는데 이를 이용하여 위상 변화에 대한 싸인과 코사인 데이터를 얻을 수 있다. 이 두 가 지 데이터를 아크탄젠트(arctangent) 연산을 통해 위상을 계산할 수 있고, 그 후에는 간단한 연산을 통해 원하는 깊이 정보를 얻을 수 있다.

TOF 센서를 이용하여 깊이 정보를 얻기 위한 가장 중요한 연산은 아크탄젠트 연산이다. 아크탄젠트 연산을 하드웨어로 구현하기 위한 방법은 다양하게 연구되고 있는데, 대표적인 방법으로는 LUT(Look-Up Table) 을 이용한 방법과 그 응용들, 다항식 근사 방법, 그리고 CORDIC 방법 등이 있다[6-12]. 본 논문에서는 다양한 아크탄젠트 연산 방법 중에서 연산이 단순하고, 적은 하드웨어로 구현이 가능한 CORDIC 알고리듬을 변형하여 연산속도를 더 높인 DCORDIC 알고리듬 기반의 위상 연산기를 설계하였다.

CORDIC 알고리듬[9]의 기본 개념은 복소평면 상에 서 주어진 벡터에 대해 각(angle)을 적당히 회전시켜 삼각함수의 값을 얻는 것이다. 이 알고리듬은 디지털 시스템에서 초월함수를 빠르게 계산하기 위해 고안되었으며, 덧셈, 뺄셈, 시프트 그리고 작은 크기의 LUT 등 단순한 회로로 구현할 수 있다는 장점을 가져, 하드웨어 구현에 널리 사용된다.

CORDIC 알고리듬은 회전 모드와 벡터링 모드로 불리는 두 가지 모드로 동작하는데, 본 논문에서는 TOF 거리 연산을 위해 필요한 벡터링 모드에 대해서만 알고리듬을 적용하여 설계한다.

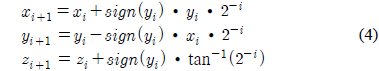

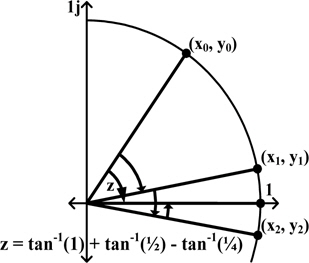

벡터링 모드를 이용한 기본 CORDIC 아크탄젠트 연산은 식 (4)와 같이 표현되며, 식 (4)는

복소평면 상에서 초기 입력 벡터는 실수부분

이와 같은 연산과정의 예를 그림 1에 나타내었다. 초기의 입력 벡터 (

첫 번째 연산에서는

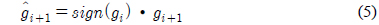

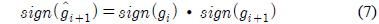

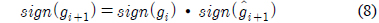

DCORDIC 알고리듬[6]에서는 기존의 식 (4)에서 새로운 임시 변수를 정의해서 새로운 식을 유도하여 사용한다. 식 (5)~(8)에서는 기존 CORDIC 식의 변수

식 (8)은 기존 변수의 부호인

CORDIC 벡터링 모드의 기본 원리는 반복적인 회전 연산을 통해 허수부분인

식 (9)를 통해 DCORDIC에서 새로운 변수 의 절대 값을 이용하여

고정 소수점 CORDIC 아크탄젠트 연산의 정확성은 입력 벡터의 실수부와 허수부, 위상 LUT의 비트 폭과 CORDIC 회전의 반복 횟수에 의해 결정된다. CORDIC 알고리듬의 반복 횟수에 따른 연산시간과 계산된 위상의 정확도 사이에 교환조건이 존재하며, 또한 내부 연산의 비트 폭에 의한 하드웨어 면적과 연산 정밀도 사 이에도 교환조건이 존재한다. 따라서 비트 폭과 반복 횟수에 따라 연산 정확도가 결정되므로, CORDIC 알고리듬의 하드웨어 구현 시에 이를 고려해야 한다.

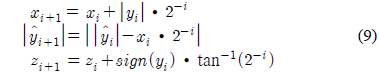

본 논문에서는 DCORDIC 기반으로 고정 소수점 연산을 수행하는 위상 연산기 하드웨어를 설계하기 위하여 기존의 연구[13]에서 도출해낸 설계사양을 이용하였다. 내부 연산의 비트 수를 16 비트 (부호 1 비트, 정수 부분 2 비트, 소수부분 13 비트), 반복 횟수 14회로 결정하였다. 결정된 설계사양을 적용한 MATLAB 시뮬레이션 결과는 그림 2와 같다. 왼쪽 그래프는 360개의 원본 데이터에 대해 DCORDIC으로 계산된 값과 일치하는 정도를 보인 것이며, 오른쪽은 각도 별 오차를 나타낸다. 최대 오차는 1.99%, 평균 오차는 0.67%로 나타나 목표 보다 우수한 정밀도가 얻어졌다.

DCORDIC 기반의 위상 연산기는 기존의 CORDIC 알고리듬에 비해 하드웨어 구조가 복잡해지고 면적이 커지는 단점이 있지만, 현재 단계의

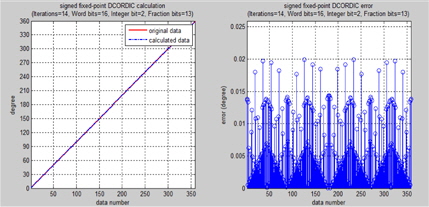

설계된 전체 위상 연산기의 하드웨어 구조는 그림 3과 같다. 입력 데이터는 전처리 블록을 통해 전처리 과정을 거친 후, 파이프라인 DCORDIC 블록으로 들어간다.

CORDIC 연산은 -90°∼90° 범위의 입력 벡터에 대해서만 위상 연산이 가능하게 설계되어, 이를 보정해 주기 위해 우선 복소 평면상에서 입력 벡터가 존재하는 사분면의 위치를

입력 벡터가 2 사분면 또는 3 사분면에 위치한 경우, 실수와 허수에 보수를 취해 각각 1 사분면과 4 사분면으로 이동시켜 CORDIC 연산을 한다. 입력 벡터의 사분면을 이동 시키는 경우에는 위상의 초기 값인

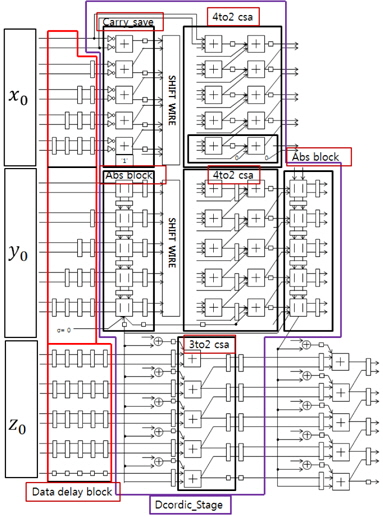

내부 DCORDIC 스테이지의 하드웨어는 그림 4와 같이 구현하였다. 반복 횟수에 해당하는 14개의 연산 스테이지로 구성되며, 각 연산 스테이지는 식 (9)의

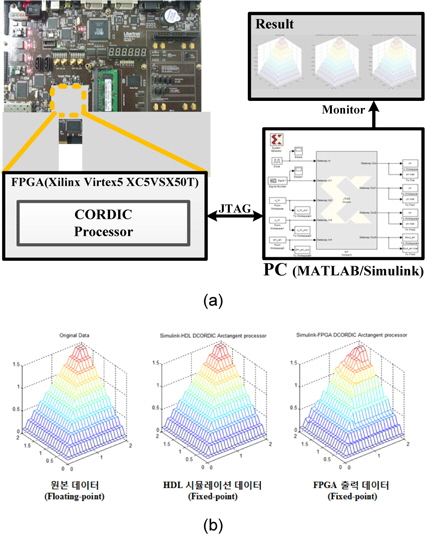

Verilog HDL로 설계된 DCORDIC 기반의 위상 연산기는 MATLAB을 이용한 입력 데이터 생성과 Modelsim을 이용한 시뮬레이션을 통해 기능 검증을 하였다. 설 계된 위상 연산기의 HDL 모델을 FPGA에 구현하고, MATLAB/Simulink와 연동시킨 FPGA-in- the-loop 환경을 통해 하드웨어 동작을 검증하였다. 그림 5(a)는 설계된 위상연산기의 FPGA 검증을 위한 FPGA-in-the-loop 환경이며, Xilinx Virtex5 XC5VSX- 50T FPGA 디바이스가 사용되었다. MATLAB에서 생성된 가상의 3차원 원본 데이터로부터 위상 연산기의 입력으로 사용 될 16 비트의 입력 벡터를 생성하였다. 생성된 벡터는 Simulink를 통해 위상 연산기가 구현된 FPGA에 인가되고, FPGA에서 출력되는 위상 데이터는 Simulink와 MATLAB을 이용하여 3차원 데이터로 복원된다. 그림 5(b)는 FPGA-in-the- loop 검증 결과를 보이고 있다.

설계된 위상연산기가 구현된 FPGA 출력 결과가 원본 데이터와 매우 잘 일치함을 확인할 수 있다. 설계된 위상 연산기는 FPGA 합성 결과 1,502 슬라이스로 구현 되었으며, 469MHz로 동작하여 469 MS/s의 성능을 갖는 것으로 평가 되었다.

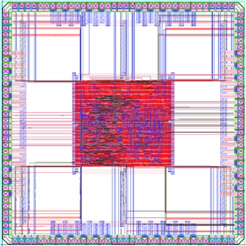

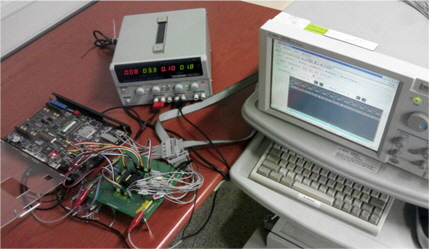

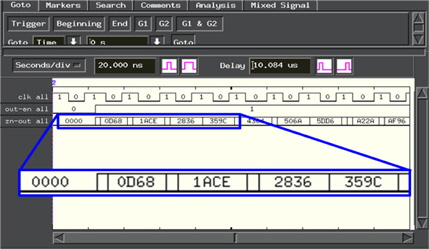

설계된 위상 연산기는 약 82,000 게이트로 구현되었으며, TSMC 0.18-㎛ CMOS 공정으로 테스트 칩을 제작하였다. 그림 6은 Cadence Virtuoso 툴을 이용하여 레이아웃 검증까지 완료된 테스트 칩의 레이아웃 도면이다. TSMC MPW로 제작된 칩을 그림 7의 테스트 시스템으로 테스트 하였다. 칩의 CORE 전압은 1.8V, IO 전압은 3.3V이고, FPGA 보드를 통해 클록과 리셋 신호가 포함된 테스트 벡터가 순차적으로 인가되도록 하였다. 24° 단위의 각도 데이터를 고정소수점 형식의 실수와 허수 값으로 생성하여 테스트 벡터로 사용하였다. Agilent 16702B 논리분석기를 사용하여 테스트 칩의 출력을 관찰하였으며, 칩 테스트 결과파형은 그림 8과 같다.

테스트 결과파형에서 볼 수 있듯이, HEX 값 0D68, 1ACE, 2836, 359C의 순서로 라디안 형태의 데이터가 출력되고, 이를 도로 변환하면 24.00379825, 47.99360828, 71.99740653, 95.98721656에 해당한다. 이는 시뮬레이션 결과와 일치하는 값이며, 제작된 칩이 높은 정밀도를 가지고 정상 동작함을 확인하였다.

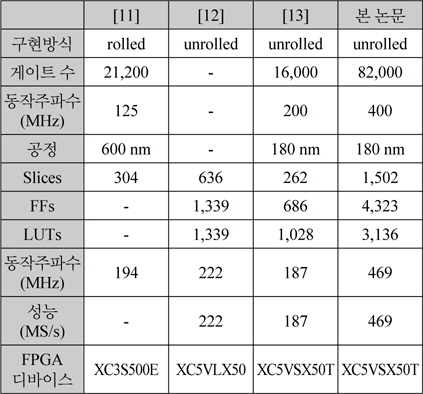

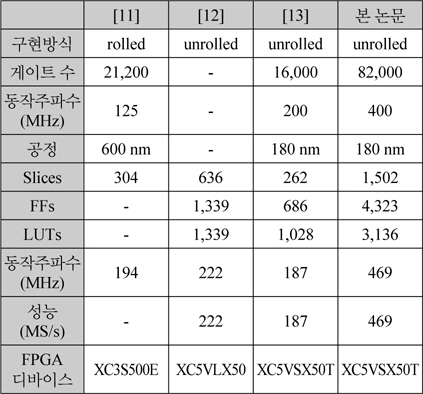

TSMC 0.18-㎛ CMOS 공정으로 설계된 DCORDIC 위상 연산기는 400MHz@1.8V로 동작하여 400 MS/s의 처리율을 갖는 것으로 평가되었다. 표 1은 타 문헌과 이전의 연구에서 구현한 CORDIC 프로세서와의 비교를 보이고 있다. 문헌 [11]은 rolled 방식으로 구현한 예이고, 문헌 [12], [13]과 본 논문의 경우는 unrolled 방식으로 구현하였다.

CORDIC 프로세서의 비교

본 논문의 위상연산기와 다른 목적으로 구현되어 정확한 비교는 할 수 없으나, 이전의 연구[13]는 16 비트의 연산을 수행하는 다른 CORDIC 프로세서들과 비교 해 보았을 때, 사용되는 로직 대비 동작주파수와 처리량이 우수한 성능을 갖는 것으로 평가 되었다. 반면 본 논문의 경우는 다른 문헌에 비해 면적이 크지만 동작주 파수와 처리량이 뛰어난 것으로 평가되었다.

3차원 영상처리용 TOF 센서의 거리 측정을 위한 DCORDIC 기반 위상 연산기를 설계하였다. 설계된 위상 연산기는 16 비트(부호 1 비트, 정수부분 2 비트, 소수부분 13 비트)의 고정 소수점 연산으로 14회의 CORDIC 스테이지 반복을 통해 위상 값을 계산한다. 0° ∼360° 범위에서 1° 단위로 계산하는 경우에, 최대 오차 1.99%, 평균 오차 0.67%의 연산 정밀도를 갖는다. 설계된 위상 연산기는 MATLAB/Simulink와 FPGA 보드를 연동시킨 FPGA-in-the-loop 환경을 통해 하드웨어 동작을 검증하였다. TSMC 0.18-㎛ CMOS 공정으로 테스트 칩을 제작하고 평가하였으며, 400MHz @1.8V로 동작하여 400 MS/s의 성능을 갖는 것으로 평가되었다.