This paper presents a 10-bit 10-MS/s asynchronous successive approximation register (SAR) analog-to-digital converter (ADC) which consists of a digital-to-analog converter (DAC), a SAR logic, and a comparator. The designed asynchronous SAR ADC with a rail-to-rail input range uses a binary weighted DAC using metal-oxide-metal (MOM) capacitor to improve sampling rate. The proposed 10-bit 10-MS/s asynchronous SAR ADC is fabricated using a 0.18-μ m CMOS process and its active area is 0.103 mm2. The power consumption is 0.37 mW when the voltage of supply is 1.1 V. The measured SNDR are 54.19 dB and 51.59 dB at the analog input frequency of 101.12 kHz and 5.12 MHz, respectively.

최근 모바일 분야에서 SoC 구현에 있어 소면적 및 저전력의 요구가 높아짐에 따라 이에 적합한 축차근사형(SAR: successive approximation register) 아날로그-디지털 변환기(ADC: analog-to-digital converter)가 주목받고 있다. 일반적으로 동기식 방식의 축차근사형 ADC는 낮은 샘플링 속도 때문에 바이오 응용 분야 혹은 센서 인터페이스 등에 주로 이용되었다. [1-4]하지만 최근에는 비동기 방식의 축차근사형 ADC가 연구되면 서 샘플링 속도를 향상시킬 수 있게 되었다[5].

동기식으로 동작하는 일반적인 축차근사형 ADC는

높은 해상도를 가진 축차근사형 ADC의 설계에 있어 샘플링 속도를 향상시키기 위한 연구는 지속되어 왔다. 가장 큰 영향을 미치는 것은 축차근사형 ADC의 구성블록 중 하나인 디지털-아날로그 변환기 (DAC: digitalto-analog converter)의 정착 시간이다. 커패시터로 구성된 DAC의 정착 시간을 줄이기 위해 다양한 연구가 진행되고 있다. 그 예로 분할-커패시터 방식의 DAC[7]을 이용하여 전체 커패시턴스를 줄이고 정착 속도를 향상시킨다. 또한 이진 여분 축차근사형 ADC[8]와 비이진 여분 축차근사형 ADC[9] 등의 구조 및 스위칭 방식을 변환하여 정착 시간을 줄이는 연구도 발표되었다. 하지만 이진 여분 방식은 추가적인 디지털 회로가 많이 요 구되어 전체 변환속도가 낮아지고 면적도 증가된다. 비이진 여분 방식은 디지털 코드로 에러를 보정하는 기법으로 추가적인 디지털 회로를 요구하지 않지만 두 개의 축차근사형 ADC가 요구되어 전력소모 및 면적에서 비효율적이다.

본 논문에서는 DAC의 커패시턴스를 줄이기 위해 MOM (metal-oxide-metal) 방식의 커패시터를 이용한 다. 커패시턴스가 작아짐에 따라 열잡음이 증가하게 되는 부분은 선형성이 좋은 바이너리 방식의 커패시터 어레이를 사용하여 보완한다.

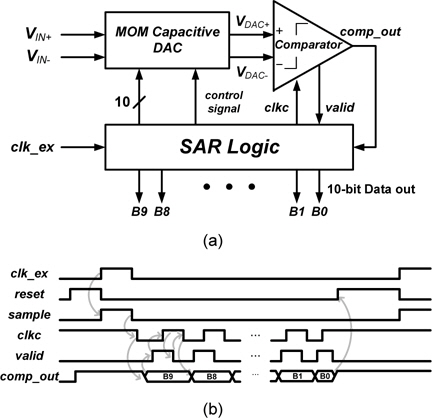

그림 1(a)는 설계된 10-bit 10-MS/s 비동기 축차근사형 ADC의 블록도로 MOM 커패시터를 이용한 DAC, 비교기, SAR 로직으로 구성된다. DAC는 차동 입력을 샘플하고 바이너리 알고리즘을 위한 기준전압을 생성한다. 비교기는 DAC의 출력전압의 차이를 비교한다. SAR 로직은 비교기의 출력을 순차적으로 저장하는 역할과 비교기의 출력 값으로부터 DAC의 스위치를 제어하는 신호를 생성한다. 비동기 축차근사형 ADC는 외부클록인

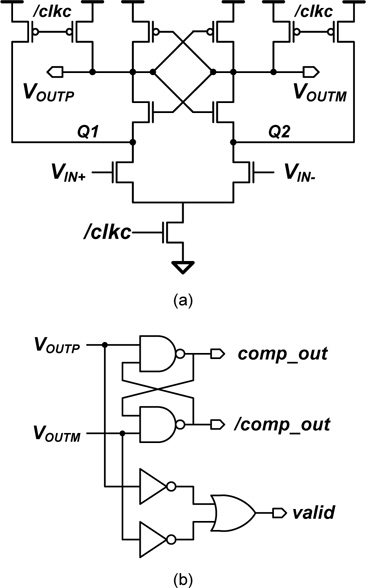

그림 2(a)는 전압 비교기의 회로도로

그림 3(a)는 MIM (metal-insulator-metal) 커패시터의 구조를 나타낸다.

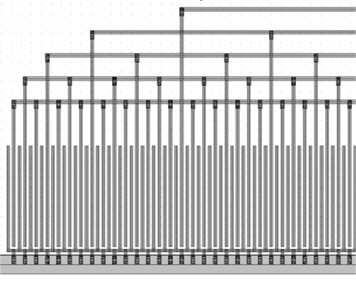

그림 4는 MOM 커패시터를 이용한 레이아웃을 나타낸다. MOM 커패시터의 좌우 대칭을 이루게 레이아웃하여 DAC의 부정합을 줄인다. 기생성분으로 커패시턴스를 생성하기 때문에 높은 값을 얻기가 어렵다. 본 논 문에서는 최소의 메탈 간격으로 설계하여 2 fF의 유닛커패시턴스를 가진다. 또한 여러 층의 MOM을 병렬로 연결할 경우 그 연결로 인한 부정합이 발생될 수 있으므로 단일 층의 MOM만 이용한다.

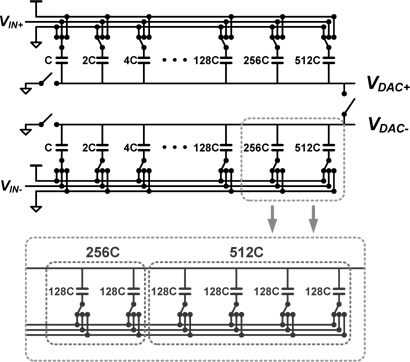

그림 5는 MOM 커패시터를 이용한 DAC의 회로도이다. 선형성이 좋은 바이너리 기반의 구조를 사용하고 MSB와 MSB-1을 결정하는 커패시터인 512C와 256C를 각각 4개와 2개의 128C로 분리함으로써 RC 지연시간을 줄여 DAC의 정착을 빠르게 한다.

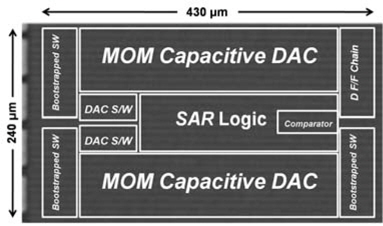

그림 6은 설계된 10-bit 10-MS/s 비동기 축차근사형ADC의 칩 사진이다. 1.1V 0.18-㎛ 1-poly 6-metal CMOS 공정에서 제작되었고 면적은 0.103 mm2이다. 전력소모는 0.37 mW이다.

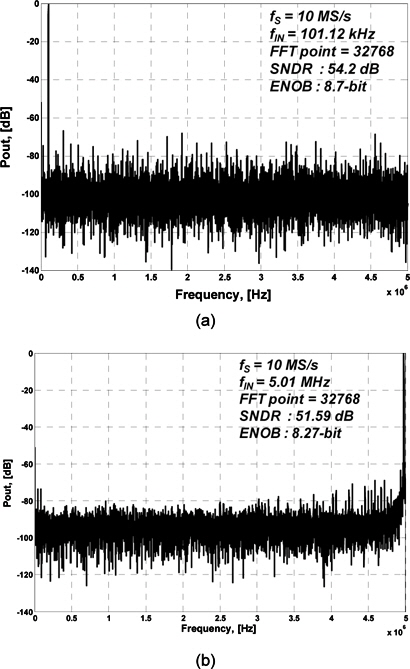

그림 7은 10 MS/s에서 101.12 kHz와 나이퀴스트(Nyquist) 입력 주파수인 5.01 MHz의 아날로그 입력 신호에 대해 측정된 ADC 출력의 FFT 결과이다. 측정된 SNDR (signal-to-noise distortion ratio)은 각각 54.2 dB와 51.6 dB이고, 그에 따른 유효비트는 각각 8.7비트와 8.3비트이다.

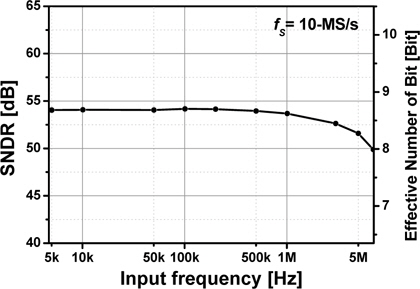

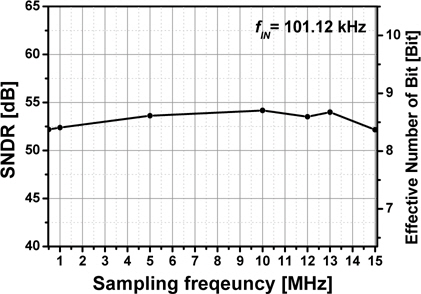

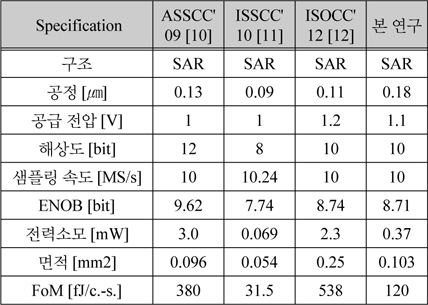

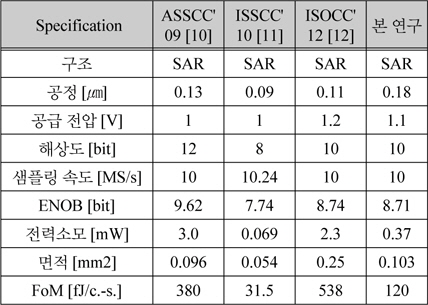

그림 8은 10 MS/s의 샘플링 속도에서 입력 주파수에 따른 SNDR을 측정한 결과이다. 낮은 주파수의 입력에 대해 약 54 dB정도를 나타났고 나이퀴스트 입력 주파수에 근접할수록 SNDR은 감소되어 7 MHz의 입력 신호에는 50 dB의 SNDR이 측정되었다. 그림 9는 101.12kHz의 아날로그 입력에서 샘플링 주파수의 변화에 따른 측정된 SNDR의 그래프이다. 측정된 SNDR은 13MHz부터 서서히 감소하였다. 14 MHz의 샘플링 주파수까지 8.5비트 이상의 유효비트를 유지하였다. 설계된 비동기 축차근사형 ADC의 요약 및 비교가 표 1에 나타난다.

축차근사형 ADC의 비교

제안하는 10비트 10-MS/s 비동기 축차근사형 ADC는 rail-to-rail의 입력 범위를 가지고 0.18-㎛ 1-poly 6-metal CMOS 공정을 사용하여 제작되었다. 축차근사형 ADC의 샘플링 속도를 향상시키기 위해 MOM 커패시터를 이용한 DAC를 사용하였고 MSB의 RC 지연시간을 줄이기 위해 MSB를 결정하는 커패시터를 병렬로 분리하여 설계하였다. 설계된 비동기 축차근사형 ADC는 101.12 kHz와 나이퀴스트 주파수인 5.01 MHz의 아날로그 입력 신호에 대해 측정된 SNDR은 각각 54.2 dB와 51.6 dB로 나타났다. 1.1 V의 공급 전압에서 전력소 모는 0.37 mW이고 면적은 0.103 mm2이다. 설계된 ADC의 FoM은 120 fJ/conversion-step이다.