This paper proposes the hardware architecture of high performance multi-mode 2D forward transform for HEVC which has same number of cycles for processing any type of four TUs and yield high throughput. In order to make the original image which has high pixel and high resolution into highly compressed image effectively, the transform technique of HEVC supports 4 kinds of pixel units, TUs and it finds the optimal mode after performs each transform computation. As the proposed transform engine uses the common computation operator which is produced by analyzing the relationship among transform matrix coefficients, it can process every 4 kinds of TU mode matrix operation with 35cycles equally. The proposed transform block was designed by Verilog HDL and synthesized by using TSMC 0.18um CMOS processing technology. From the results of logic synthesis, the maximum operating frequency was 400MHz and total gate count was 214k gates which has the throughput of 10-Gpels/cycle with the 4k(3840x2160) @30fps image.

최근 UHD(Ultra High Definition) TV와 디지털 영상 기술의 발전과 방송 기술의 발전과 함께 고화질, 고해 상도의 영상 서비스들이 TV가 아닌 모바일 기기까지 확대되고 있다. 또한 기존의 2D를 뛰어 넘은 3D 비디오 영상 보급도 확대됨에 따라 고해상도, 고화질의 영상에 대한 필요성이 대두되고 있다. 이를 배경으로 많은 데 이터양을 갖는 영상을 전송하기 위하여 기존의 영상 분야에서 많이 쓰이고 있는 영상 압축 코덱인 H.264/AVC의 압축률보다 두 배 이상의 높은 압축률을 목표로 ISO/IEC MPEG과 ITU-T VCEG에서는 JCT-VC(Joint Collaborative Team on Video Coding)을 만들어 차세대 영상 압축 코덱인 HEVC(High Efficiency Video Coding)에 대하여 2010년 4월 회의를 시작으로 표준화 회의를 시작하였으며, 최근 표준을 제정하였다.

HEVC는 압축 효율을 높이기 위해 CU(Coding Unit), PU(Prediction Unit), TU(Transform Unit)와 같은 다양한 블록을 지원하며, 각 블록들 또한 다양한 사이즈를 지원하고 있다[1]. H.264/AVC에 비해 2~4배 증가된 다양한 사이즈의 블록을 사용하기 때문에 내부 연산의 복잡도와 연산 수행 시간이 증가하였다[2].

본 논문에서는 4가지의 TU(4x4, 8x8, 16x16, 32x32)를 각 모드마다 변환 연산을 수행하여 최적의 모드를 찾는 HEVC의 변환기의 특성을 배경으로 행렬 계수들간의 관계를 분석하여 공통 연산기를 통해 병렬적인 구조로 변환 행렬 연산을 수행함으로써 4가지의 TU 변환 연산을 동일한 사이클로 처리가 가능한 구조의 HEVC고성능 다중모드 2D 변환기를 제안한다.

제안하는 고성능 다중모드 2D 변환기는 TSMC 180nm CMOS 공정 라이브러리를 사용해 합성한 결과 4k(3840x2160)@30fps 영상을 기준으로 최대 동작주파수는 400MHz이고 총 게이트 수는 214k가 소요되었다. 또한 처리량은 10-Gpels/cycle이다.

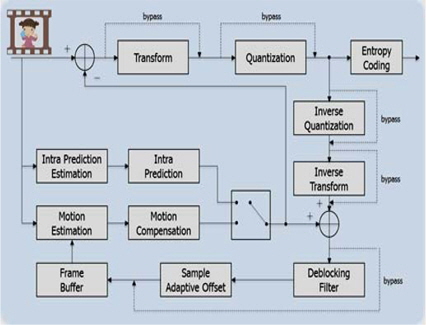

HEVC는 기존의 국제 표준인 H.264/AVC의 구조와 비슷하다. 그림 1은 HEVC의 부/복호기의 구조이다. 하지만 고해상도, 고화질의 영상을 상대로 높은 압축 효율을 얻기 위해 쿼드트리 기반 부호화 기술을 사용한다. 또한, DCT(Discrete Cosine Transform)로 인해 생기는 블록 경계의 왜곡을 제거하기 위하여 기존의 디블록킹 필터보다 연산 과정을 간략화한 기술인 디블록킹 필터를 사용한다[3]. 부호화 과정을 통해 발생하는 원본 영상과 부호화 영상간의 왜곡을 화소 단위의 오프셋을 통해 보상하여 주관적 화질 및 부호화 효율을 향상시키는 기술인 SAO(Sample Adaptive Offset)을 적용시켰다[4].

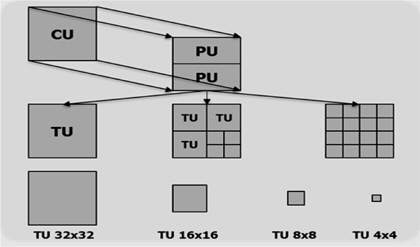

HEVC의 쿼드트리 기반 부호화 기술은 그림 2와 같다. 블록들은 CU(Coding Unit), TU(Transform Unit), PU(Prediction Unit)으로 분류된다[5]. HEVC의 변환기는 원본 영상 데이터와 예측 영상 데이터 간의 공간적 영역의 오차 데이터인 다양한 PU를 입력 받아 주파수 영역의 데이터로 바꾸는 작업을 수행한다.

이로 인해 변환기는 4가지 TU 모드(4x4, 8x8, 16x16, 32x32)에 대한 변환 행렬 연산을 각각 수행하여 최적의 TU 모드를 찾는다.

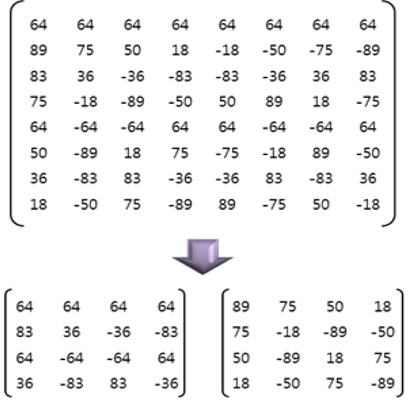

차세대 영상 압축 코덱인 HEVC의 변환기는 Chen’s fast DCT 알고리즘을 기반으로 둔 기법을 사용하여 버터플라이 구조를 가진다[6]. 그림 3은 8x8 TU 모드의 변환 행렬을 Chen’s 고속 DCT 기법에 적용시켜 두 개의 4x4 변환 행렬로 재구성한 예이다.

8x8 TU 모드의 변환 행렬을 반으로 나누면 짝수 행은 y축 반전이 된 값과 같고, 홀수 행은 y축 반전과 부호를 반대로 한 값과 같다. 이러한 특성을 바탕으로 홀수와 짝수 변환 계수로 나뉜 두 개의 4x4 행렬로 재구성할 수 있다[7].

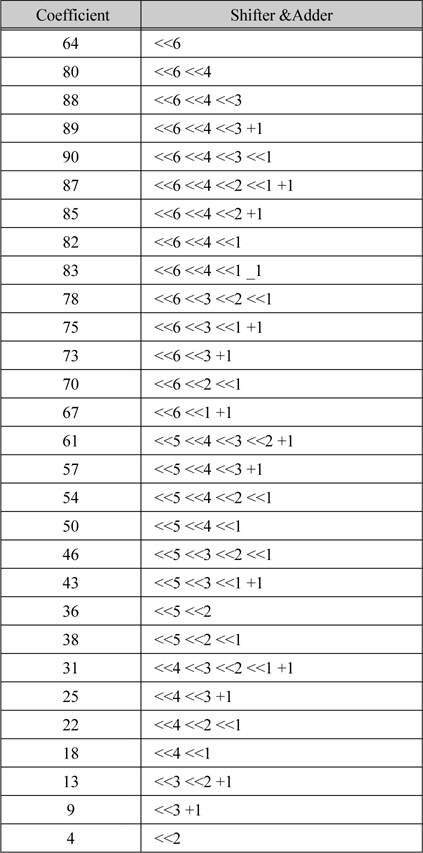

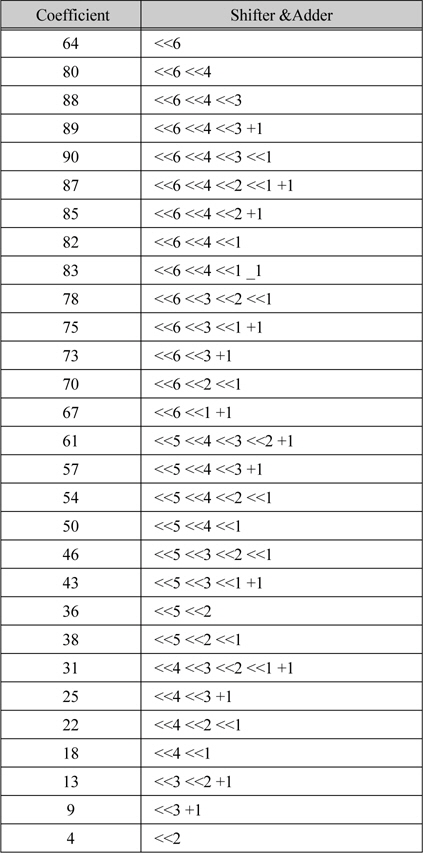

본 논문에서 제안하는 HEVC 변환기의 구조는 하나의 변환 행렬을 짝수와 홀수 행렬로 나누는 방식인 Chen’s 고속 DCT 알고리즘에 기반하여 설계되었다. 변환 행렬은 4x4~16x16 크기 TU 모드의 행렬 계수들이 32x32 크기 TU 모드의 행렬 계수의 부분 집합인 특징을 갖는다. 이를 기반으로 제안하는 변환 블록은 최적화된 공통 연산기를 사용하여 모든 행렬 계수에 대한 변환 행렬 연산을 수행할 수 있는 구조로 설계하였다. 표 1은 공통 연산기를 구현하기 위하여 사용한 변환 행렬 계수들의 특징이다.

변환 행렬 계수 간의 관계

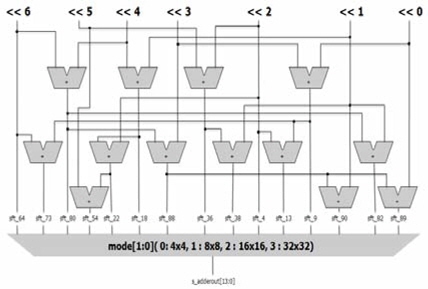

구현된 공통 연산기는 <<6, <<5, <<4,<<3, <<2, <<1 총 6개의 쉬프트와 <<0, 1개의 덧셈기로 구성된다. 그림 4는 변환 행렬 계수간의 관계를 분석하여 구성한 공통 연산기의 구조이다.

구성한 공통 연산기는 TU 모드에 대한 제어 신호 및 입력 영상 데이터를 입력 받아 6개의 쉬프트에 대한 연산을 수행한 후 1 개의 덧셈기를 통해 변환 행렬 계수에 대한 행렬 연산을 수행한다.

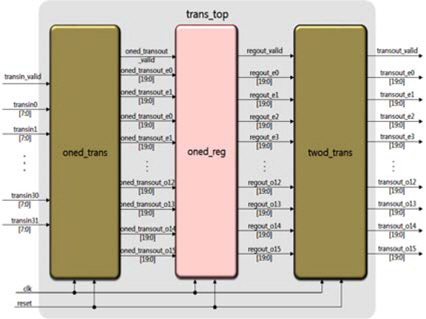

그림 5는 제안하는 HEVC 변환기의 전체 하드웨어 구조이다.

1D 변환기와 2D 변환기 역할을 하는 oned_trans, twod_trans와 변환기 메모리 역할을 하는 oned_reg로 구성된다. oned_trans와 twod_trans는 앞에서 언급한 것과 같이 공통 연산기를 사용한 구조이며, TU 모드에 대한 값과 병렬적으로 입력 영상 데이터들을 받아 TU 모드에 맞는 변환 행렬 연산을 수행하여 값을 출력하는 기능을 한다. oned_reg는 1D 변환기(oned_trans)에서 출력된 데이터를 입력받아 2D 변환기(twod_trans)로 보내주기 위해 저장된 데이터들을 하나씩 쉬프트해주는 기능을 한다.

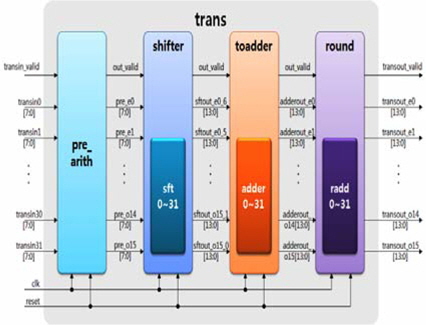

제안하는 HEVC 변환기의 내부 구조는 그림 6과 같다. pre_arith, shifter, toadder, round 모듈로 구성된다.

pre_arith 모듈은 행렬 연산 전에 수행하는 전처리를 담당하며, shifter 모듈은 행렬 연산의 곱셈 부분에 해당하고 곱셈기보다 연산 시간 및 하드웨어 면적이 적은 쉬프트로 구현되어있다. toadder 모듈은 행렬 연산 위치에 맞게 shifter 모듈의 출력 값을 선택하여 덧셈을 수행한다. round 모듈은 toadder 모듈의 출력 값을 반올림하여 데이터의 손실을 최소화하는 기능을 담당한다.

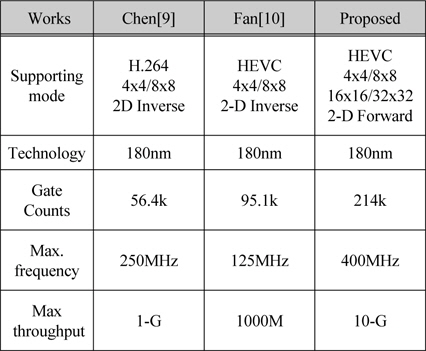

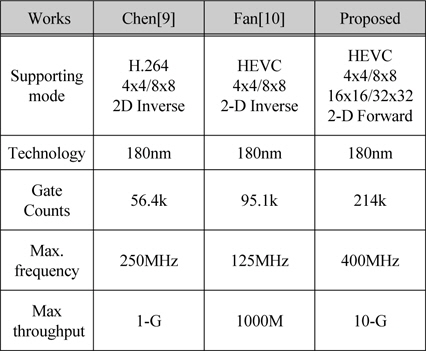

본 논문에서 제안하는 HEVC 변환 블록은 표준 참조 소프트웨어인 HM-10.0rc1을 이용하여 검증하였다[8]. HM-10.0rc1의 변환 블록을 통과하기 전과 후의 영상 데이터를 추출하여 제안하는 변환 블록을 시뮬레이션한 결과를 파일로 생성하여 비교하였다. 또한 IDEC에서 제공하는 Synopsys사의 Design Compiler를 통해 TSMC 180nm CMOS 공정 라이브러리로 합성한 결과, 4k(3840x2160)@30fps 영상을 기준으로 최대 동작 주파수는 400MHz이고 총 게이트 수는 214k이다. 표 2는 기존의 변환 블록의 구조와 제안하는 변환 블록의 구조를 비교한 것이다. 기존의 변환 블록 구조들은 대부분 역변환 블록에 대하여 다루어지기 때문에 제안하는 변환 블록의 구조를 기존의 역변환 블록들과 비교하였다. 비교한 결과로 총 게이트의 수는 기존의 연구보다 3~4배 정도 늘었지만 처리량은 10배 이상 좋아짐을 확인할 수 있다.

기존 구조와 제안한 구조와의 비교

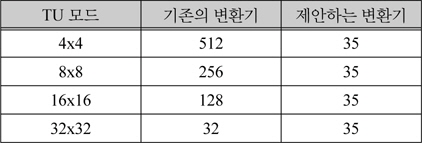

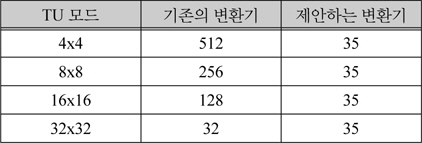

표 3은 기존 변환기가 1D 변환을 할 경우, 32x32 크기의 TU 모드에서 한 라인을 1사이클에 처리한다고 가정하였을 때 나머지 TU 모드를 처리하는데 걸리는 사이클 수를 나타낸 것이다.

[표 3.] TU 모드 별 1D 변환 연산 처리 사이클 수

TU 모드 별 1D 변환 연산 처리 사이클 수

기존 변환기는 각 TU 모드 별 변환 행렬 연산을 처리하는데 걸리는 사이클 수가 다르며, 32x32 크기의 TU 모드에 대한 변환 행렬 연산을 처리하기 위해서 32사이클, 16x16크기의 TU 모드의 경우 128사이클, 8x8크기의 TU 모드의 경우 256사이클, 4x4모드의 경우 512사이클이 소요된다. 제안하는 변환기는 TU 모드에 영향을 받지 않고 모든 변환 행렬 연산을 처리하는데 동일하게 35사이클이 소요된다.

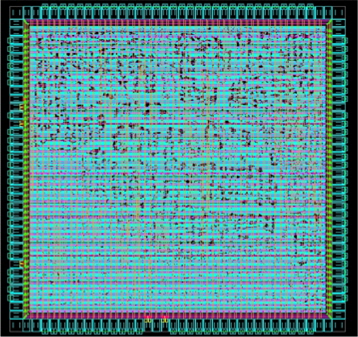

그림 7은 제안하는 변환기를 TMSC 180nm CMOS 공정 라이브러리를 사용하여 Synopsys사의 IC Compiler를 통해 Layout한 화면이다. 칩 사이즈는 3mm× 3mm이다.

본 논문에서 제안하는 HEVC 변환 블록은 4개의 TU 모드(4x4, 8x8, 16x16, 32x32)를 지원하며, 행렬 계수의 특징을 사용하여 공통 연산기를 통해 입력 영상 데이터에 대한 모든 행렬 계수 연산을 수행한다. 모든 TU 모드의 변환 행렬 연산을 처리하는데 걸리는 사이클은 35사이클로 동일하다. 제안하는 HEVC 변환 블록의 하드웨어 구조를 합성한 결과 총 게이트 수는 214k로 이전 연구에 비해 3~4배정도 늘었으나 처리량은 10-Gpels/cycle로 이전 연구에 비해 10배정도 증가하여 효율성을 높였다. 최대 동작주파수는 400MHz이다.