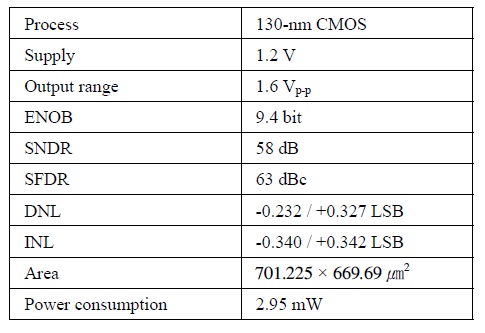

This paper proposes 5-MS/s 10-bit digital-to-analog converter(DAC) with the improved linearity. The proposed DAC consists of a 10-bit R-2R-based DAC, an output buffer using a differential voltage amplifier with rail-to-rail input range, and a band-gap reference circuit for the bias voltage. The linearity of the 10-bit R-2R DAC is improved as the resistor of 2R is implemented by including the turn-on resistance of an inverter for a switch. The output voltage range of the DAC is determined to be 2/3×VDD from an rail-to-rail output voltage range of the R-2R DAC using a differential voltage amplifier in the output buffer. The proposed DAC is implemented using a 1-poly 8-metal 130nm CMOS process with 1.2-V supply. The measured dynamic performance of the implemented DAC are the ENOB of 9.4 bit, SNDR of 58 dB, and SFDR of 63 dBc. The measured DNL and INL are less than +/-0.35 LSB. The area and power consumption of DAC are 642.9 × 366.6 ㎛2 and 2.95 mW, respectively.

최근 digital television(DTV)로의 전환 후 지역별로 활용 가능한 TV 유휴대역(TVWS : TV white space)을 활용하여 주파수 이용효율을 높이고, 창의적 전파이용 확대하여 무선트래픽 급증을 해결하고자 한다. 이에 따라 1GHz이하 대역의 신호 처리가 가능한 RF chip의 개발이 요구된다. 또한 최근 스마트기기의 발달로 다양한 기능의 integrated circuit(IC)들이 system on chip(SoC)으로 설계가 이루어지고 있으며, 이에 따라 각 블록들의 저전력, 소면적화가 요구되는 상황이다.

본 논문에서는 TVWS의 활용을 위한 통신 SoC에서 송신 단에 이용되는 1 ~ 5MHz의 샘플링 주파수를 가지고 선형성을 개선시킨 10bit 디지털/아날로그 변환기를 제안한다. 제안하는 디지털/아날로그 변환기는 R-2R 구조를 사용하여 저전력, 소면적의 설계를 가능하게 한다[1-4]. R-2R구조의 디지털/아날로그 변환기에서 스위칭 동작을 위해 사용되는 인버터의 turn-on저항을 계산하여 이 값을 저항 열에 포함시켜 디지털/아날로그 변환기의 선형성을 개선시킨다. 또한 출력버퍼로 사용되는 전압증폭기를 rail-to-rail 구조로 설계 하여 800mV 큰 출력 전압범위를 가지도록 설계한다[5]. 본 논문의 II장에서는 제안하는 디지털/아날로그 변환기의 구조를 소개하며, III장에서는 디지털/아날로그 변환기의 구체적인 회로를 소개한다. IV 장에서는 디지털/아날로그 변환기의 구현 및 측정결과를 보여주며, V장에서 본 논문의 결론을 맺는다.

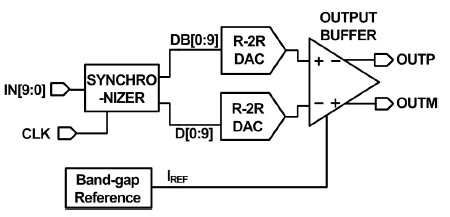

그림 1은 제안된 디지털/아날로그 변환기의 전체 블록도이다. 디지털/아날로그 변환기는 플립-플롭으로 구성된 동기화 회로, R-2R 디지털/아날로그 변환기, 밴드-갭 기준전압 회로, 그리고 차동 전압증폭기를 이용한 출력버퍼로 구성된다. 입력받은 10bit의 디지털 입력 코드 (IN[9:0])는 동기화 회로를 통해 D[0:9] 신호와 이의 반전 신호인 DB[0:9] 디지털 코드를 생성한다. D[0:9]와 DB[0:9] 신호는 각각의 R-2R 디지털/아날로그 변환기를 통해 rail-to-rail의 아날로그 신호로 변환되고, 변환된 아날로그 신호는 전압증폭기로 구성된 출력버퍼를 통해 peak-to-peak 1.6VDIFF로 감소되어 출력된다.

디지털/아날로그 변환기의 선형성을 개선하기 위해 R-2R 디지털/아날로그 변환기에 스위칭 동작을 위해 사용되는 인버터의 turn-on 저항을 고려하여 설계하였으며, 출력버퍼는 rail-to-rail 입력전압 범위를 가지는 전압증폭기를 이용하여 설계되었다.

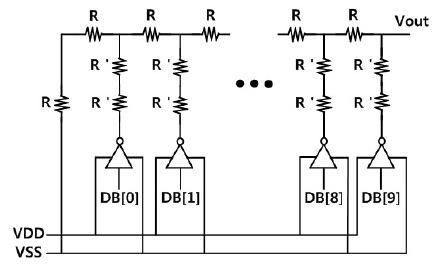

R-2R 디지털/아날로그 변환기 구조는 그림 2와 같이 R과 2R이 병렬로 연결된다. 본 설계에서 사용된 단위저항 R의 값은 9kΩ이고, 2R을 구성하는 저항

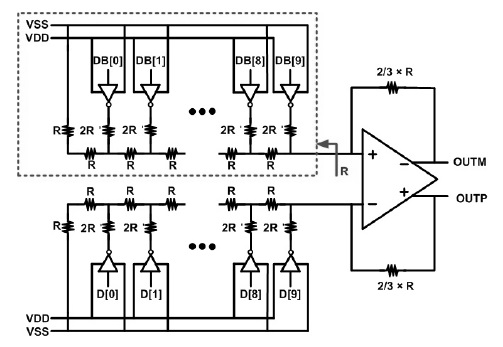

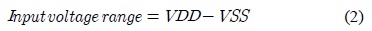

그림 3은 차동 전압증폭기를 이용한 출력버퍼의 회로이다. 출력전압의 범위가 1.2V인 R-2R 디지털/아날로그 변환기의 등가저항은 단위저항 R이다. 출력전압 범위를 단일 출력 기준 800mV로 맞추기 위해 차동 전압증폭기의 피드백 저항을

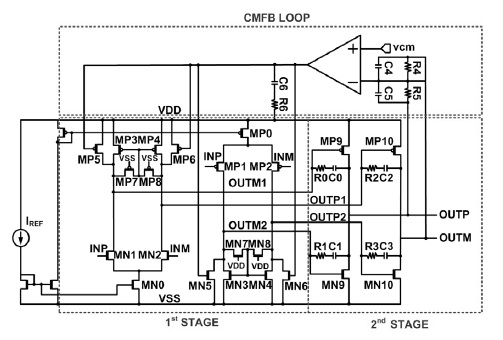

Rail-to-rail의 입력전압 범위를 가지는 차동 전압증폭기를 위해 입력 단을 NMOS (

차동 전압증폭기의 공통모드 전압을 일정하게 유지하기 위해 common mode feedback (CMFB) 기법을 사용하였다.

그림 5는 밴드-갭 기준전압 회로도이다[6]. 밴드-갭 기준전압을 통해 차동 전압증폭기의 바이어스 전압을 공급하기위한 전류(IREF)와 CMFB를 위한 공통모드 전압 (Vcm)을 공급한다.

밴드-갭 기준전압의 면적을 줄이기 위해 PTAT와 CTAT성분을 만드는 BJT에 흐르는 전류인

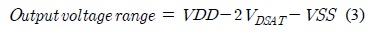

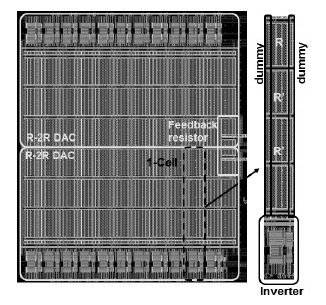

제안된 디지털/아날로그 변환기는 1.2V 공급전압, 1-poly 8-metal를 이용하는 130nm CMOS 공정에서 제작되었다. 그림 6 (a), (b)는 디지털/아날로그 변환기의 레이아웃과 칩 사진이며, 면적은 366.6 × 642.9㎛2이며 전력소모는 2.95mW이다.

그림 7은 R-2R DAC이 저항 배열을 보여주기 위해 그림 6(a)의 R-2R 디지털/아날로그 변환기의 레이아웃을 확대하여 나타낸 것이다. 디지털/아날로그 변환기의 저항의 부정합을 최소화하기 위해 인버터와

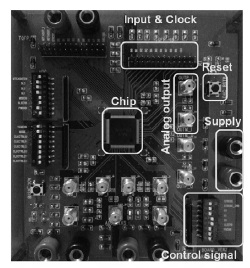

그림 8은 디지털/아날로그 변환기를 측정하기 위해 FR-4, 6-layer로 제작된 테스트 보드이다.

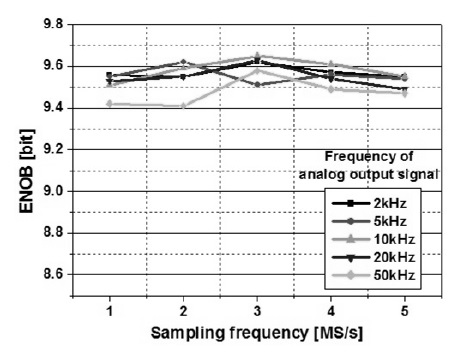

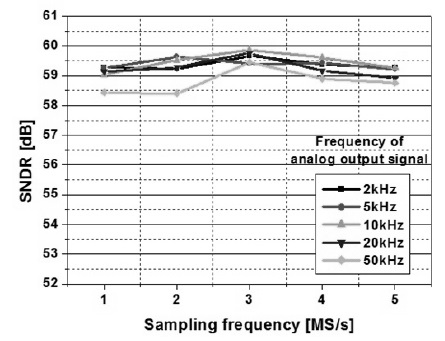

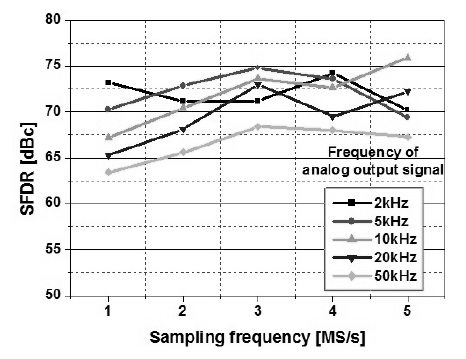

그림 9는 샘플링 주파수가 1MS/s이고, 입력신호 주파수가 5kHz일 때 측정된 power spectral density의 파형이다. 유효비트(effective number of bit: ENOB)는 9.54bit, spurious-free dynamic range (SFDR)은 73.03dBc, signal to noise-plus-distortion ratio (SNDR)은 59.25dB이다. 그림 10~12는 입력신호 주파수와 샘플링 주파수의 변화에 따른 디지털/아날로그 변환기의 ENOB와 SNDR, SFDR을 나타낸 그래프이다. 설계된 디지털/아날로그 변환기의 ENOB는 9.4bit, SNDR은 58dB, SFDR은 63dBc 이상으로 유지되는 것을 확인할 수 있다.

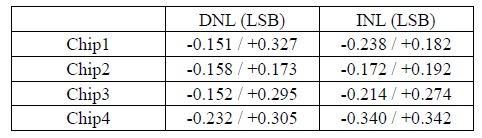

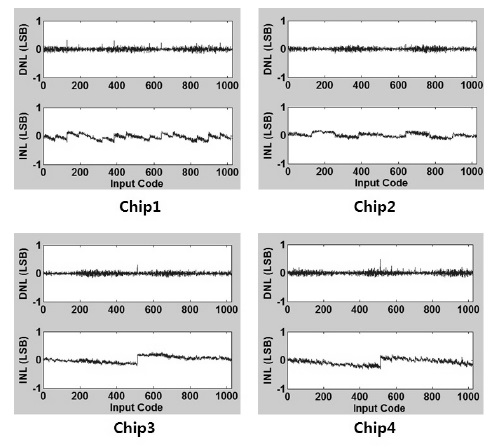

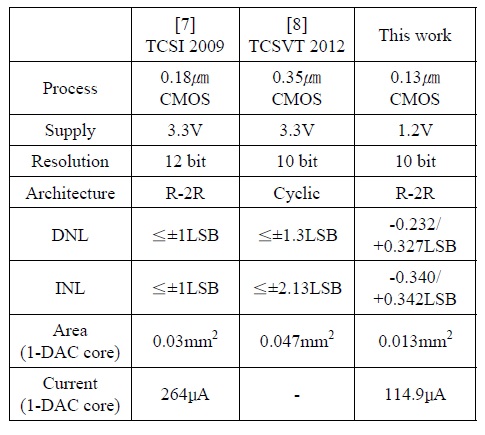

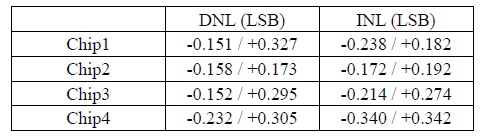

표 1과 그림 13은 설계된 디지털/아날로그 변환기 4개의 칩을 측정하여 구한 DNL과 INL을 나타낸 파형과 최대/최소값이다. 설계된 디지털/아날로그 변환기의 1least significant bit (LSB)는 1.56mV이며, 4개의 칩 중 differential non-linearity (DNL)의 최대치는 -0.232/+0.305 LSB이고, integral non-linearity (INL)의 최대값은 -0.340/+0.342 LSB로 나타남을 그림 14를 통해 확인할 수 있다. 그림 13에서 chip3과 chip4의 INL 파형을 보면 512code 또는 값이 급격하게 변화는 것을 확인할 수 있는데, 이것은 저항의 부정합에 의한 영향으로 나타나는 현상이다. 하지만 이 값의 변화는 최대 0.342LSB 이고, 이는 0.53mV에 해당하는 값이다. 표 2는 제작된 디지털/아날로그 변환기의 성능을 요약한 표이다.

[표 1.] 측정된 디지털/아날로그 변환기의 DNL/INL

측정된 디지털/아날로그 변환기의 DNL/INL

디지털/아날로그 변환기의 성능

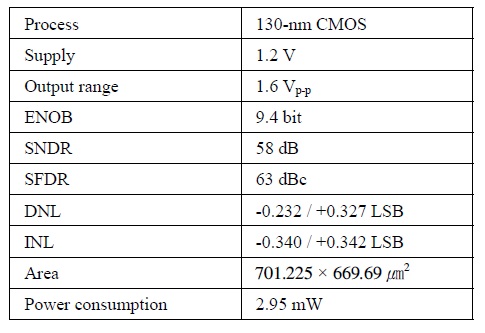

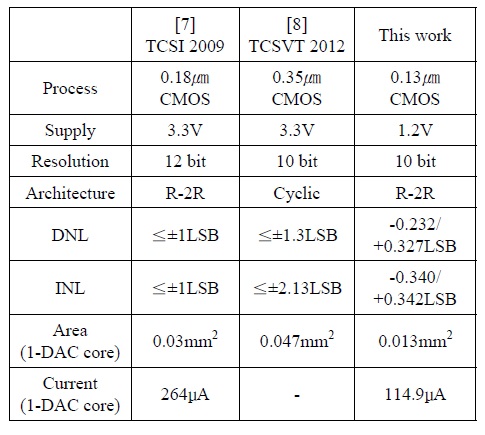

표 3은 제안된 디지털/아날로그 변환기와 비슷한 성능을 가지는 최근 발표된 타 논문의 디지털/아날로그 변환기와의 성능을 비교한 표이다. 제안된 디지털/아날로그 변환기와의 특성을 비교해봤을 때, 변환기의 선형성 부분에서 크게 개선되어 나타나는 것을 알 수 있고, 디지털/아날로그 변환기 core 하나의 면적을 비교하였을 때, 본 연구에서 설계된 R-2R 디지털/아날로그 변환기가 가장 작은 것으로 나타났다.

[표 3.] 최근 발표된 디지털/아날로그 변환기의 성능 비교

최근 발표된 디지털/아날로그 변환기의 성능 비교

제안된 디지털/아날로그 변환기는 1.2V 공급전압, 1-poly 8-metal의 130nm CMOS 공정으로 제작되었다. R-2R 디지털/아날로그 변환기 구조를 이용하며, R-2R 디지털/아날로그 변환기의 2R 구현에 스위치를 위해 사용되는 인버터의 turn-on 저항 값을 포함하여 설계함으로 선형성을 개선시켰다. 디지털/아날로그 변환기의 면적은 366.61 × 642.94㎛2이며 전력소모는 2.95mW 이다. 샘플링 주파수가 1~5MHz이며 이 주파수 대역에서 동적 특성으로 ENOB는 9.4bit, SNDR은 58dB, SFDR은 63dBc 이상으로 나타난다. INL/DNL은 모두 +/-0.35LSB 이하로 측정되었다.