This paper proposes a hardware architecture for high performance Deblocking filter(DBF) in High Efficiency Video Coding for UHD(Ultra High Definition) videos. This proposed hardware architecture which has less processing time has a 4-stage pipelined architecture with two filters and parallel boundary strength module. Also, the proposed filter can be used in low-voltage design by using clock gating architecture in 4-stage pipeline. The segmented memory architecture solves the hazard issue that arises when single port SRAM is accessed. The proposed order of filtering shortens the delay time that arises when storing data into the single port SRAM at the pre-processing stage. The DBF hardware proposed in this paper was designed with Verilog HDL, and was implemented with 22k logic gates as a result of synthesis using TSMC 0.18um CMOS standard cell library. Furthermore, the dynamic frequency can process UHD 8k(7680×4320) samples@60fps using a frequency of 150MHz with an 8K resolution and maximum dynamic frequency is 285MHz. Result from analysis shows that the proposed DBF hardware architecture operation cycle for one process coding unit has improved by 32% over the previous one.

HEVC는 ITU-T와 ISO/IEC가 공동으로 제정 완료한 고해상도 및 고화질 영상을 위한 비디오 압축 코덱으로 압축 효율을 높이기 위해 CU(Coding Unit), PU(Prediction Unit), TU(Transform Unit)와 같은 다양한 블록을 지원하며 각각 블록에서 다양한 사이즈를 지원하고 있다. 디블록킹 필터는 CU내의 PU 및 TU에서 예측 및 양자화로 인해 발생하는 블록 경계의 왜곡을 효과적으로 제거함으로써 주관적 화질 및 객관적 화질을 향상시키는 기술이다. 최근 광대역 전송의 발전과 함께 차세대 영상 기기에 대한 관심이 증가하면서 UHD급 이상의 고화질 영상에 대한 수요가 증가하고 있다[1].

본 논문에서는 UHD 영상을 위한 고성능 HEVC 디블록킹 필터 하드웨어 구조를 제안한다. 제안하는 하드웨어 구조는 필터링 수행시간 단축을 위해 두 개의 필터로 구성된 4단 파이프라인 구조와 경계강도 모듈을 병렬적인 구조로 설계하였다. 또한 저전력 하드웨어 구조를 위해 파이프라인의 단계를 클록 게이팅으로 설계하였고, 파이프라인 과정에서 단일 포트 SRAM에 접근할 때 발생하는 해저드 문제를 해결하기 위해 분할된 메모리 구조로 설계하였다.

본 논문의 구성은 다음과 같다. 2장에서는 HEVC의 기존 디블록킹 필터 기술에 대해 기술하고, 3장에서는 제안하는 디블록킹 필터 하드웨어 구조를 기술한다. 4장에서는 하드웨어 구현 결과 및 성능 비교에 대해 기술하고, 5장에서 본 연구의 결론을 도출한다.

블록화 현상은 예측 및 양자화에 의해 발생하기 때문에 PU 및 TU 경계 모두에서 디블록킹 필터링이 수행되어야 한다. H.264/AVC 표준은 PU 크기보다 TU 크기가 클 수 없기 때문에 TU경계에서만 디블록킹 필터링을 수행하면 PU 경계를 포함하여 디블록킹 필터링을 자동적으로 수행할 수 있다. 그러나 HEVC의 화면간 예측 모드인 경우, PU 크기보다 TU 크기가 클 수 있으므로 TU 경계에 대해서만 디블록킹 필터링을 수행할 경우 PU 경계를 위한 디블록킹 필터링이 수행 되지 않는 경우가 발생한다. 따라서 HEVC 디블록킹 필터링은 PU 및 TU 경계 모두에서 수행된다. 또한 H.264/AVC 표준은 4×4 크기의 TU만을 사용하므로 수평 또는 수직 방향으로 4×4 화소 단위의 필터링 유닛만을 정의하고 있으나[2], HEVC는 수평 또는 수직 방향으로 8×8 화소 단위의 필터링 유닛을 정의함으로써 디블록킹 필터링의 복잡도를 간략화 시켰다. 영상의 해상도가 증가하고, 예측의 성능이 향상되면서 잔여 신호의 발생량이 감소하기 때문에 블록화 현상 또한 감소할 것이라는 일반적인 사실에 근거로 8×8 화소 단위의 필터링 유닛은 디블록킹 필터링의 복잡도를 감소 시켰다. 따라서 8×8 화소 이하의 PU 또는 TU 경계에서는 디블록킹 필터링을 수행하지 않는다.

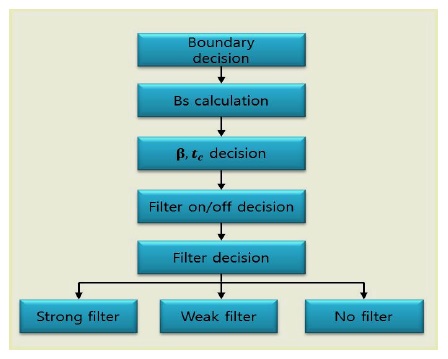

HEVC 디블록킹 필터의 필터링 알고리즘은 그림 1과 같이 여섯 단계로 구성되어 있다.

디블록킹 필터의 첫 번째 단계인 Boundary decision은 디블록킹 필터를 적용하기 위한 경계 위치를 결정한다. 단, 첫 번째 단계에서 필터링이 필요한 위치만을 결정하는 것이며, 실제 필터링의 수행 여부는 네 번째 단계인 필터 온/오프 단계에서 결정된다. 디블록킹 필터를 위한 경계의 종류는 CU 경계, PU 경계, TU 경계 세 가지로 나눠진다. 하나의 CU 경계는 PU 또는 TU 경계가 되기 때문에 필터링을 수행해야 하는 경계 대상이다. 두 번째 단계인 Bs Calculation은 경계 강도 결정 단계이며 경계에 인접한 블록의 특성에 따라 다른 강도의 디블록킹 필터를 수행하기 위해 경계 강도 BS(Boundary Strength)를 결정한다. 세 번째 단계인 Decision of β, tc 단계는 필터링 수행 여부 및 필터링 선택 등의 임계값으로 사용되는 β와 tc를 결정한다. 네 번째 단계인 Filter on/off decision 단계는 필터링 유닛 단위로 필터링 수행 여부를 결정한다. 다섯 번째 단계인 Filter decision 단계는 필터링 선택을 통해 Strong filter 혹은 Weak filter를 결정한다. 여섯 번째 단계는 픽셀 데이터를 정해진 필터로 필터링 수행한다[3].

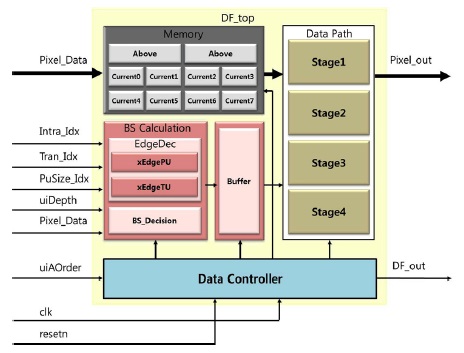

제안하는 UHD 영상을 위한 고성능 HEVC 디블록킹 필터 하드웨어 구조는 필터 수행 시간을 단축하기 위해 두 개의 필터로 구성된 4단 파이프라인 구조와 경계 강도 모듈을 병렬적인 구조로 설계하였다. 또한 저전력 하드웨어 구조를 위해 파이프라인의 단계를 클록 게이팅으로 설계하였고, 파이프라인에서 단일 포트 SRAM에 접근할 때 발생하는 해저드 문제를 해결하기 위해 분할된 메모리 구조로 설계하였다. 그림 2는 제안하는 하드웨어 구조를 나타낸 것이다.

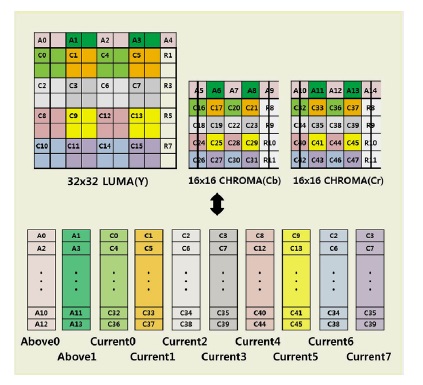

제안하는 하드웨어 구조는 기본적으로 32×32 크기의 quarter LCU단위로 필터링을 수행하며, 필터링에 사용될 상위 픽셀 및 현재 픽셀이 저장될 Memory, 필터링 연산을 담당하는 두 개의 필터와 클록 게이팅을 사용한 4단 파이프라인 Data Path 모듈, 경계강도를 계산하는 BS Decision 모듈, 전반적인 데이터를 컨트롤하는 Data Controller 모듈로 구성된다.

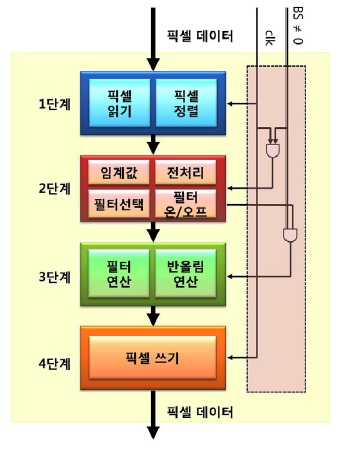

연속적인 필터링 과정에서 두 개의 필터링 오퍼레이션 사이의 데이터 의존성이 없다면 파이프라인 구조가 적용 될 수 있다. 따라서 본 논문에서는 HEVC 디블록킹 필터의 처리율 향상을 위해 최적화된 4단 파이프라인 구조를 제안한다. 그림 3은 제안하는 4단 파이프라인 구조이다.

제안하는 필터의 4단 파이프라인은 메모리 읽기, 임계값 및 전처리, 필터 연산, 메모리 쓰기로 구성된다. 첫 번째 단계인 메모리 읽기 단계에서는 메모리로부터 필터링을 위한 픽셀 데이터를 읽고, 정렬한 후 다음 단계로 픽셀 데이터를 할당한다. 파이프라인의 각 단계마다 추가적인 컨트롤 신호를 사용하여 클록 게이팅을 적용함으로써 전력소모를 감소시켰다. 만약 현재의 BS값이 0이라면 이어지는 파이프라인 단계는 모두 NOP(No-Operation)로 처리된다. 두 번째 단계인 임계값 계산 및 전처리 단계는 필터링 온/오프의 조건을 검사하기 위해 룩업테이블을 참조하여 β와 tc값을 결정하고 세 번째 단계인 필터 연산 단계의 연산 부담을 줄여주기 위해 강한 필터와 약한 필터의 조건에 사용할 수식의 일부를 미리 계산한다. 또한 강한 필터와 약한 필터 중 어느 필터로 필터링 할지를 선택한다. 만약 필터링 온/오프에서 오프일 경우, 세 번째 단계가 NOP로 처리된다. 세 번째 단계인 필터 연산 단계에서는 계산된 임계값과 경계 강도에 따라 입력된 픽셀들을 각기 다른 탭의 필터를 적용하여 연산하며 완료된 데이터는 마지막 네 번째 단계인 메모리 쓰기 단계에서 다음 필터링에 사용하기 위해 메모리에 저장한다.

4단 파이프라인 구조의 첫 번째와 마지막 단계는 메모리에서 픽셀을 읽어 오거나 저장하는 단계로서 매 클록마다 픽셀 데이터를 패치하고 필터링 되지 않더라도 이후 동작을 위해 외부 메모리에 저장해야 하므로 항상 활성화 된다. 두 번째 단계에서는 앞단에서 계산된 경계 강도 값이 0일 경우 필터링을 수행하지 않으므로 클록을 비활성화 한다. 세 번째 단계에서도 마찬가지로 경계 강도 값이 0일 경우 클록을 비활성화하며 추가적으로 두 번째 단계에서 계산된 필터링 온/오프조건을 검사하여 오프 조건일 경우에도 클록을 비활성화 한다. 제안하는 구조에서는 클록 게이팅 인에이블 신호의 타 이밍 안정화를 위해 래치-기반 클록 게이팅 회로를 사용하였다.

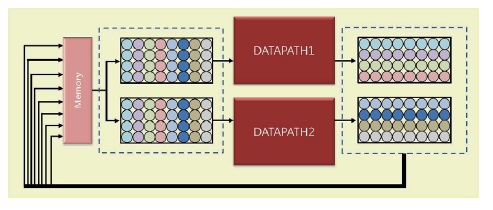

그림 4는 파이프라인에서 사용된 두 개의 필터 구조이다. 기존 HEVC 디블록킹 필터는 8×8블록에서 상위 4×8블록을 먼저 필터링한 후 나머지 4×8블록을 필터링 한다. HEVC 디블록킹 필터는 적응적으로 필터링이 처리되기 때문에 병렬적으로 필터링을 실행할 수 있다. 제안하는 디블록킹 필터는 수직 에지의 경계면을 먼저 필터링하고 수평 에지의 경계면을 필터링 해야한다. 그림 4는 8×8블록의 한 경계면을 두번에 나눠서 처리하지 않고 두 개의 필터를 사용하여 한 번에 8×8 블록의 경계면을 처리하는 것을 나타낸다. 메모리에서 읽어온 8×8 블록을 4×8 블록으로 각각 DATAPATH1과 DATAPATH2에 입력된다. 각각의 DATAPATH에서 파이프라인으로 필터링 된 후 다시 메모리로 출력된다.

디블록킹 필터의 파이프라인 구조에서 발생하는 해저드는 모두 메모리 접근 동작의 경우 발생한다. 따라서 제안하는 하드웨어 구조는 분할된 메모리 구조를 사용함으로써 해저드 문제를 해결할 수 있다.

제안하는 디블록킹 필터의 메모리는 10개의 단일 포트 메모리 구조이다. 현재 픽셀에 대한 메모리 8개(Current0~7), 상위 픽셀에 대한 메모리 2개(Above9~1)를 사용하여 메모리를 교차로 읽기/쓰기 함으로써 이중 포트 메모리를 사용하지 않고 해저드를 해결할 수 있다. 그림 5은 제안하는 메모리 구조를 나타낸다.

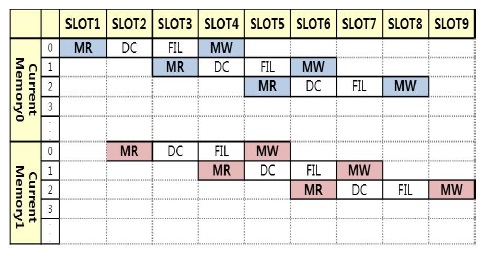

해저드 문제는 4단 파이프라인에서 쓰기와 읽기가 한 메모리에서 동시에 실행될 때 발생한다. 제안하는 분할된 메모리로 해저드를 해결할 수 있다. 그림 6은 4단 파이프라인의 메모리 수행 과정을 나타낸다. 그림 6과 같이 각 파이프라인 연산을 통해 메모리 접근이 각각 다르다는 것을 알 수 있다. Current memory0은 슬롯 1에서 메모리 읽기를 하고 슬롯 3에서 다시 메모리 읽기를 한다. 한 슬롯을 건너뛰는 동작을 하기 때문에 동시에 메모리 읽기와 메모리 쓰기를 하는 경우가 없다. 따라서 제안하는 분할된 메모리 구조를 이용하여 해저드 문제를 해결할 수 있다.

BS 결정 모듈은 적은 연산기와 비교기들로 설계를 할 수 있다. 경계 강도 결정 모듈의 수행 사이클은 전체 수행 사이클에 많은 수행 사이클을 차지한다. 32×32 픽셀을 필터링하는데 106 사이클이 필요하고 BS 결정 모듈은 32 사이클을 차지한다. BS 결정 모듈이 전체 필터링 수행 사이클의 약 30%를 차지한다. BS 결정 모듈의 병렬 설계로 로직 게이트는 적게 증가하고 전체 수행 사이클 수는 대폭 줄일 수 있다. 병렬적인 BS 결정 모듈에 인해 전체 수행 사이클인 106 사이클에서 75 사이클로 수행 사이클을 감소 할 수 있다.

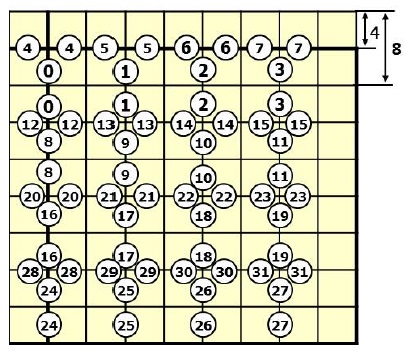

제안하는 필터링 순서는 디블록킹 필터의 앞부분에서 디블록킹 필터의 메모리에 데이터가 저장될 때 발생하는 지연 시간을 줄일 수 있다. 그림 7은 제안하는 필터링 순서를 나타낸다. 그림 7의 원안에 있는 번호는 필터링 순서를 나타내고 번호 순서대로 필터링을 수행한다.

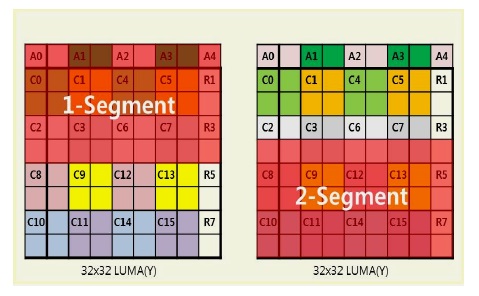

그림 8은 필터링 순서에 따른 메모리 처리 과정을 나타낸다. Current Pixel memory 부분에서 1-Segment를 필터링한 후 2-Segment를 필터링 수행할 때 1-Segment는 디블록킹 필터 앞단에서 디블록킹 필터의 참조 메모리로 데이터를 저장한다.

1-Segment가 필터링할 때에는 2-Segment의 메모리에 데이터를 저장한다. 이와 같은 동작으로 참조 메모리가 저장될 때 생기는 지연시간을 감소시킬 수 있다.

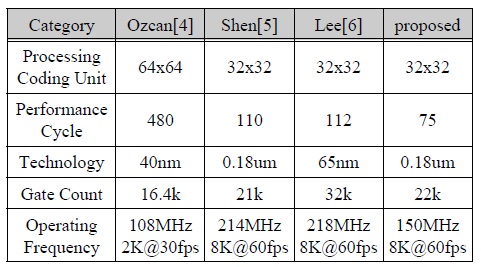

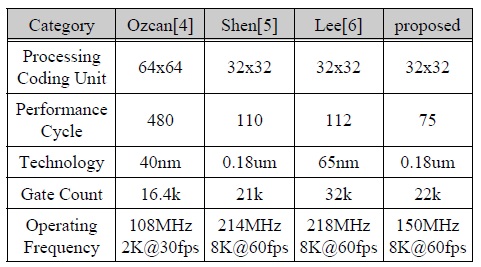

본 논문에서 제안하는 디블록킹 필터는 Verilog HDL로 설계한 RTL 코드를 TSMC 0.18um CMOS 공정의 라이브러리를 사용하여 IDEC에서 지원하는 Synopsys 사의 Design Compiler를 통해 합성하였다. 합성한 결과 총게이트 수는 22k이고 제안한 구조는 32×32 처리 코딩 유닛을 75 수행 사이클로 필터링 한다. UHD급 8k(7680×4320)@60fps 영상을 동작 주파수 150MHz로 처리하며 최대 동작주파수는 285MHz이다. 표 1은 기존에 제안되었던 디블록킹 필터의 합성 결과와 제안하는 디블록킹 필터의 합성 결과를 비교한 것이다.

[표 1.] 기존에 제안된 DBF 구조와 제안한 DBF 구조의 비교 결과

기존에 제안된 DBF 구조와 제안한 DBF 구조의 비교 결과

기존 제안된 Shen[5]는 32×32 처리 코딩 유닛을 110 수행 사이클로 필터링 하고 8k(7680×4320)@ 60fps 영상을 동작 주파수 214MHz로 처리하였다. TSMC 0.18um CMOS로 합성한 결과 제안한 구조의 로직 게이트 수는 22k, Shen[5]의 로직 게이트 수는 21k이다. 따라서 로직 게이트 수는 Shen[5]의 구조와 비교하여 0.05% 증가한 반면 필터링 수행 사이클은 32% 감소하여 처리율이 향상된 것을 확인할 수 있다. Ozcan[4]과 Lee[6]는 공정이 다르지만 공정크기를 감안해 비교하여 제안하는 하드웨어 구조가 더 적은 게이트수를 사용 되었다 판단되고, 수행 사이클이 더 적음을 확인하였다.

본 논문에서는 UHD 영상을 위한 고성능 HEVC 디블록킹 필터의 하드웨어 구조를 제안한다. 제안하는 디블록킹 필터 하드웨어 구조는 필터링 수행시간 단축을 위한 4단 파이프라인 구조와 적은 연산량을 가진 경계 강도 결정 모듈 및 두 개의 필터를 사용하여 병렬 구조로 설계 하였다. 또한 4단 파이프라인의 각 단계마다 클록 게이팅을 적용하여 전력 소모를 감소시켰다. 파이프라인 과정에서 발생하는 해저드 문제를 해결하기 위해 분할된 메모리 구조를 설계하였다. 또한, 메모리에 픽셀 데이터를 저장하기 위한 과정에서 발생하는 지연시간을 줄이기 위해 새로운 필터링 순서를 제안한다.

제안하는 디블록킹 필터는 HM10을 참고하였다[7,8]. Verilog HDL로 설계하였으며 TSMC 0.18um CMOS 공정을 이용해 합성한 결과 22k의 로직 게이트로 구현 되었다. 또한 수행 사이클은 32x32(qLCU)를 75 사이클로 필터링을 하고, 동작 주파수는 150MHz에서 8K 해상도인 7680×4320@60fps 처리가 가능하다. 따라서 제안하는 디블록킹 하드웨어 구조는 기존 제안된 Shen[5]보다 처리율이 32% 향상되었다.

최근 Many Core Processing 및 알고리즘에 대한 논문들이 나오고 있다[9,10]. 향후 Many Core Processing 및 알고리즘과 하드웨어 최적화에 대해 연구할 계획이다.